Chapter 5 Configuration Register

5-11

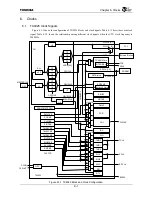

5.2.8

DMA Request Control Register (DRQCTR)

0xE024

31

16

Reserved

:

Type

: Initial value

15 12

11 8 7 4 3 0

DMAREQ[3] DMAREQ[2] DMAREQ[1] DMAREQ[0]

R/W

R/W

R/W

R/W

:

Type

0x0 0x0 0x0 0x0

:

Initial

value

Bits Mnemonic Field

Name

Description

31:16

⎯

Reserved

⎯

15:12

DMAREQ[3]

DMA Request 3

DMA Request 3 (Initial value: 0x0, R/W)

This field selects the DMA request source of DMAREQ[3].

0xxx: reserved

1000: SIO ch0. Receive

1001: SIO ch1 Receive

1010: SIO ch0. Transmit

1011: SIO ch1 Transmit

1100: ACLC ch0

1101: ACLC ch1

1110: ACLC ch2

1111: ACLC ch3

11:8

DMAREQ[2]

DMA Request 2

DMA Request 2 (Initial value: 0x0, R/W)

This field selects the DMA request source of DMAREQ[2].

0xxx: reserved

1000: SIO ch0. Receive

1001: SIO ch1 Receive

1010: SIO ch0. Transmit

1011: SIO ch1 Transmit

1100: ACLC ch0

1101: ACLC ch1

1110: ACLC ch2

1111: ACLC ch3

7:4

DMAREQ[1]

DMA Request 1

DMA Request 1 (Initial value: 0x0, R/W)

This field selects the DMA request source of DMAREQ[1].

0xxx: DMAREQ[1] (external signal)

1000: SIO ch0. Receive

1001: SIO ch1 Receive

1010: SIO ch0. Transmit

1011: SIO ch1 Transmit

1100: ACLC ch0

1101: ACLC ch1

1110: ACLC ch2

1111: ACLC ch3

3:0

DMAREQ[0]

DMA Request 0

DMA Request 0 (Initial value: 0x0, R/W)

This field selects the DMA request source of DMAREQ[0].

0xxx: DMAREQ[0] (external signal)

1000: SIO ch0. Receive

1001: SIO ch1 Receive

1010: SIO ch0. Transmit

1011: SIO ch1 Transmit

1100: ACLC ch0

1101: ACLC ch1

1110: ACLC ch2

1111: ACLC ch3

Figure 5.2.8 DMA Request Control Register (DRQCTR)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...