Section 14 Direct Memory Access Controller (DMAC)

Rev.1.00 Dec. 13, 2005 Page 602 of 1286

REJ09B0158-0100

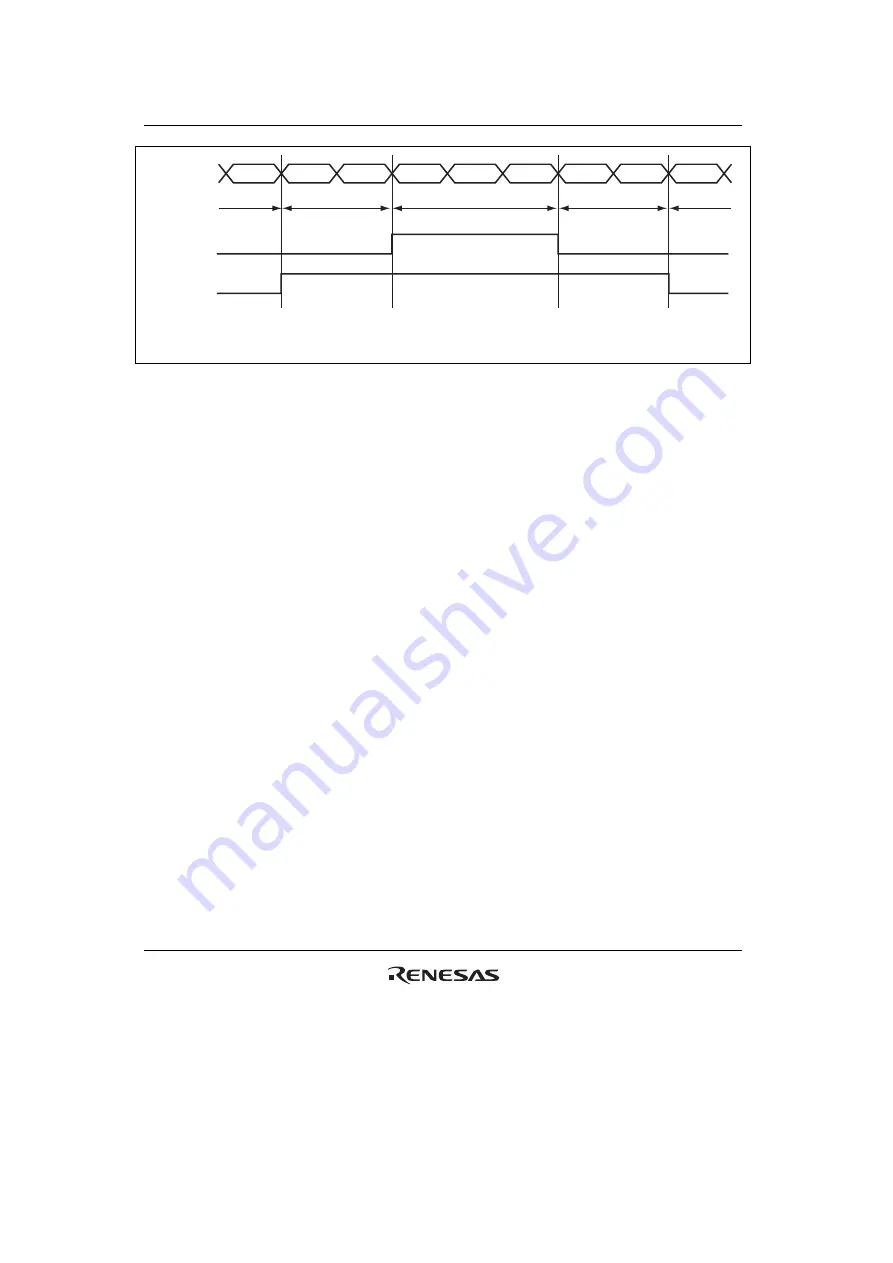

DMA CH1

Burst mode

Priority:

CH0:

CH1:

CH0 > CH1

Cycle steal mode

Burst mode

DMA CH0 and CH1

Burst mode

DMA CH1

Burst mode

CH0 transfer

source

SuperHyway

bus cycle

CH1 transfer

source

CPU

DMA CH1

DMA CH1

DMA CH0

DMA CH1

DMA CH0

DMA CH1

DMA CH1

CPU

Figure 14.10 Bus State when Multiple Channels are Operating

In round-robin mode, the priority changes according to the specification shown in figure 14.2.

However, the channel in cycle steal mode cannot be mixed with the channel in burst mode.

14.4.4

DMA Transfer Flow

After the DMA source address registers (SAR), DMA destination address registers (DAR), DMA

transfer count registers (DMATCR), DMA channel control registers (CHCR), DMA operation

register (DMAOR), and DMA extended resource selectors (DMARS) are set, the DMAC transfers

data according to the following procedure:

1. Checks to see if transfer is enabled (DE = 1, DME = 1, TE = 0, AE = 0, NMIF = 0)

2. When a transfer request occurs while transfer is enabled, the DMAC transfers one transfer unit

of data (depending on the TS0 and TS1 settings). In auto request mode, the transfer begins

automatically when the DE bit and DME bit are set to 1. The DMATCR value will be

decremented for each transfer. The actual transfer flows vary by address mode and bus mode.

3. When the specified number of transfer have been completed (when DMATCR reaches 0), the

transfer ends normally. If the IE bit in CHCR is set to 1 at this time, a DMINT interrupt is sent

to the CPU.

4. When an address error or an NMI interrupt is generated, the transfer is aborted. Transfers are

also aborted when the DE bit in CHCR or the DME bit in DMAOR is changed to 0.

Figure 14.11 shows a flowchart of this procedure.

Summary of Contents for SH7780 Series

Page 2: ...Rev 1 00 Dec 13 2005 Page ii of l ...

Page 28: ...Rev 1 00 Dec 13 2005 Page xxviii of l ...

Page 50: ...Rev 1 00 Dec 13 2005 Page l of l ...

Page 82: ...Section 1 Overview Rev 1 00 Dec 13 2005 Page 32 of 1286 REJ09B0158 0100 ...

Page 122: ...Section 3 Instruction Set Rev 1 00 Dec 13 2005 Page 72 of 1286 REJ09B0158 0100 ...

Page 146: ...Section 4 Pipelining Rev 1 00 Dec 13 2005 Page 96 of 1286 REJ09B0158 0100 ...

Page 196: ...Section 6 Floating Point Unit FPU Rev 1 00 Dec 13 2005 Page 146 of 1286 REJ09B0158 0100 ...

Page 292: ...Section 9 L Memory Rev 1 00 Dec 13 2005 Page 242 of 1286 REJ09B0158 0100 ...

Page 492: ...Section 12 DDR SDRAM Interface DDRIF Rev 1 00 Dec 13 2005 Page 442 of 1286 REJ09B0158 0100 ...

Page 674: ...Section 15 Clock Pulse Generator CPG Rev 1 00 Dec 13 2005 Page 624 of 1286 REJ09B0158 0100 ...

Page 692: ...Section 16 Watchdog Timer and Reset Rev 1 00 Dec 13 2005 Page 642 of 1286 REJ09B0158 0100 ...

Page 726: ...Section 18 Timer Unit TMU Rev 1 00 Dec 13 2005 Page 676 of 1286 REJ09B0158 0100 ...

Page 1032: ...Section 25 Audio Codec Interface HAC Rev 1 00 Dec 13 2005 Page 982 of 1286 REJ09B0158 0100 ...

Page 1150: ...Section 28 General Purpose I O GPIO Rev 1 00 Dec 13 2005 Page 1100 of 1286 REJ09B0158 0100 ...

Page 1184: ...Section 29 User Break Controller UBC Rev 1 00 Dec 13 2005 Page 1134 of 1286 REJ09B0158 0100 ...

Page 1266: ...Section 31 Electrical Characteristics Rev 1 00 Dec 13 2005 Page 1216 of 1286 REJ09B0158 0100 ...

Page 1328: ...Appendix Rev 1 00 Dec 13 2005 Page 1278 of 1286 REJ09B0158 0100 ...

Page 1336: ...Rev 1 00 Dec 13 2005 Page 1286 of 1286 REJ09B0158 0100 ...

Page 1339: ......

Page 1340: ...SH7780 Hardware Manual ...