8XC196NT USER’S MANUAL

B-8

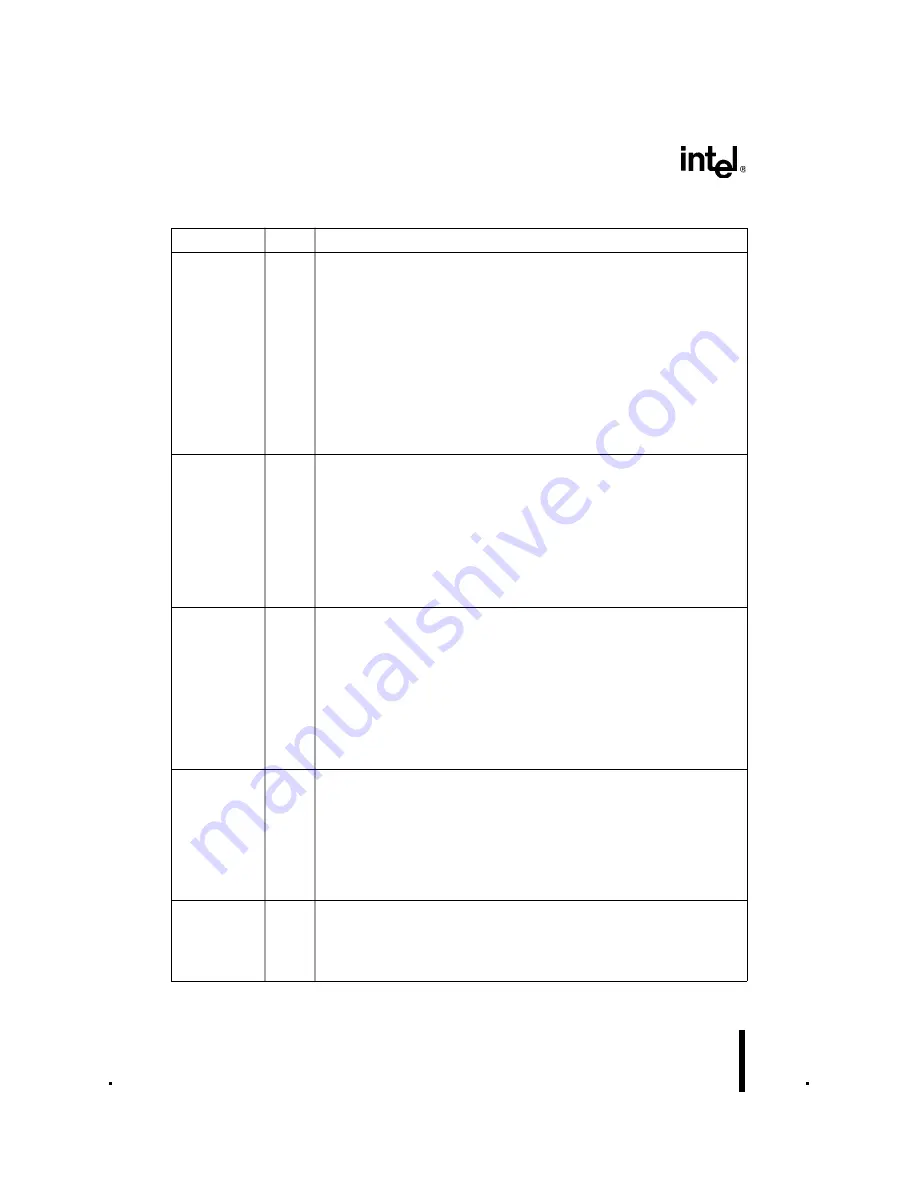

INTOUT#

O

Interrupt Output

This active-low output indicates that a pending interrupt requires use of the

external bus. How quickly the 8XC196NT

asserts INTOUT# depends upon the

status of HOLD# and HLDA# and whether the device is executing from internal

or external program memory. If the 8XC196NT receives an interrupt request

while it is in hold and it is executing code from internal memory, it asserts

INTOUT# immediately. However, if the 8XC196NT is executing code from

external memory, it asserts BREQ# and waits until the external device

deasserts HOLD# to assert INTOUT#. If the 8XC196NT is executing code from

external memory and it receives an interrupt request as it is going into hold

(between the time that an external device asserts HOLD# and the time that the

8XC196NT responds with HLDA#), the 8XC196NT asserts both HLDA# and

INTOUT# and keeps them asserted until the external device deasserts HOLD#.

INTOUT is multiplexed with P2.4 and AINC#.

NMI

I

Nonmaskable Interrupt

In normal operating mode, a rising edge on NMI causes a vector through the

NMI interrupt at location FF203EH. NMI must be asserted for greater than one

state time to guarantee that it is recognized.

In idle mode, a rising edge on the NMI pin causes the device to return to normal

operation, where the first action is to execute the NMI service routine. After

completion of the service routine, execution resumes at the instruction following

the IDLPD instruction that put the device into idle mode.

In powerdown mode, a rising edge on the NMI pin does not cause the device to

exit powerdown.

ONCE#

I

On-circuit Emulation

Holding ONCE# low during the rising edge of RESET# places the device into

on-circuit emulation (ONCE) mode. This mode puts all pins into a high-

impedance state, thereby isolating the device from other components in the

system. The value of ONCE# is latched when the RESET# pin goes inactive.

While the device is in ONCE mode, you can debug the system using a clip-on

emulator. To exit ONCE mode, reset the device by pulling the RESET# signal

low. To prevent inadvertent entry into ONCE mode, either configure this pin as

an output or hold it high during reset and ensure that your system meets the V

IH

specification (see datasheet).

ONCE# is multiplexed with P2.6.

P0.7:4

I

Port 0

This is a high-impedance, input-only port. Port 0 pins should not be left floating.

These pins may individually be used as analog inputs (ACH

x

) or digital inputs

(P0.

x

). While it is possible for the pins to function simultaneously as analog and

digital inputs, this is not recommended because reading port 0 while a

conversion is in process can produce unreliable conversion results.

ANGND and V

REF

must be connected for port 0 to function.

P0.7:4 are multiplexed with ACH7:4 and PMODE.3:0.

P1.7:0

I/O

Port 1

This is a standard, bidirectional port that is multiplexed with individually

selectable special-function signals.

Port 1 is multiplexed as follows: P1.0/EPA0, P1.1/EPA1, P1.2/EPA2,

P1.3/EPA3, P1.4/T1CLK, P1.5/T1DIR, P1.6/T2CLK, and P1.7/T2DIR.

Table B-4. Signal Descriptions (Continued)

Name

Type

Description

Summary of Contents for 8XC196NT

Page 1: ...8XC196NT Microcontroller User s Manual...

Page 2: ...8XC196NT Microcontroller User s Manual June 1995 Order Number 272317 003...

Page 22: ...1 Guide to This Manual...

Page 23: ......

Page 35: ......

Page 36: ...2 Architectural Overview...

Page 37: ......

Page 49: ......

Page 50: ...3 Programming Considerations...

Page 51: ......

Page 66: ...4 Memory Partitions...

Page 67: ......

Page 104: ...5 Standard and PTS Interrupts...

Page 105: ......

Page 147: ......

Page 148: ...6 I O Ports...

Page 149: ......

Page 176: ...7 Serial I O SIO Port...

Page 177: ......

Page 194: ...8 Synchronous Serial I O SSIO Port...

Page 195: ......

Page 211: ......

Page 212: ...9 Slave Port...

Page 213: ......

Page 231: ......

Page 232: ...10 Event Processor Array EPA...

Page 233: ......

Page 270: ...11 Analog to digital Converter...

Page 271: ......

Page 291: ......

Page 292: ...12 Minimum Hardware Considerations...

Page 293: ......

Page 306: ...13 Special Operating Modes...

Page 307: ......

Page 317: ......

Page 318: ...14 Interfacing with External Memory...

Page 319: ......

Page 362: ...15 Programming the Nonvolatile Memory...

Page 363: ......

Page 408: ...A Instruction Set Reference...

Page 409: ......

Page 476: ...B Signal Descriptions...

Page 477: ......

Page 493: ......

Page 494: ...C Registers...

Page 495: ......

Page 565: ......

Page 566: ...Glossary...

Page 567: ......

Page 580: ...Index...

Page 581: ......

Page 597: ......