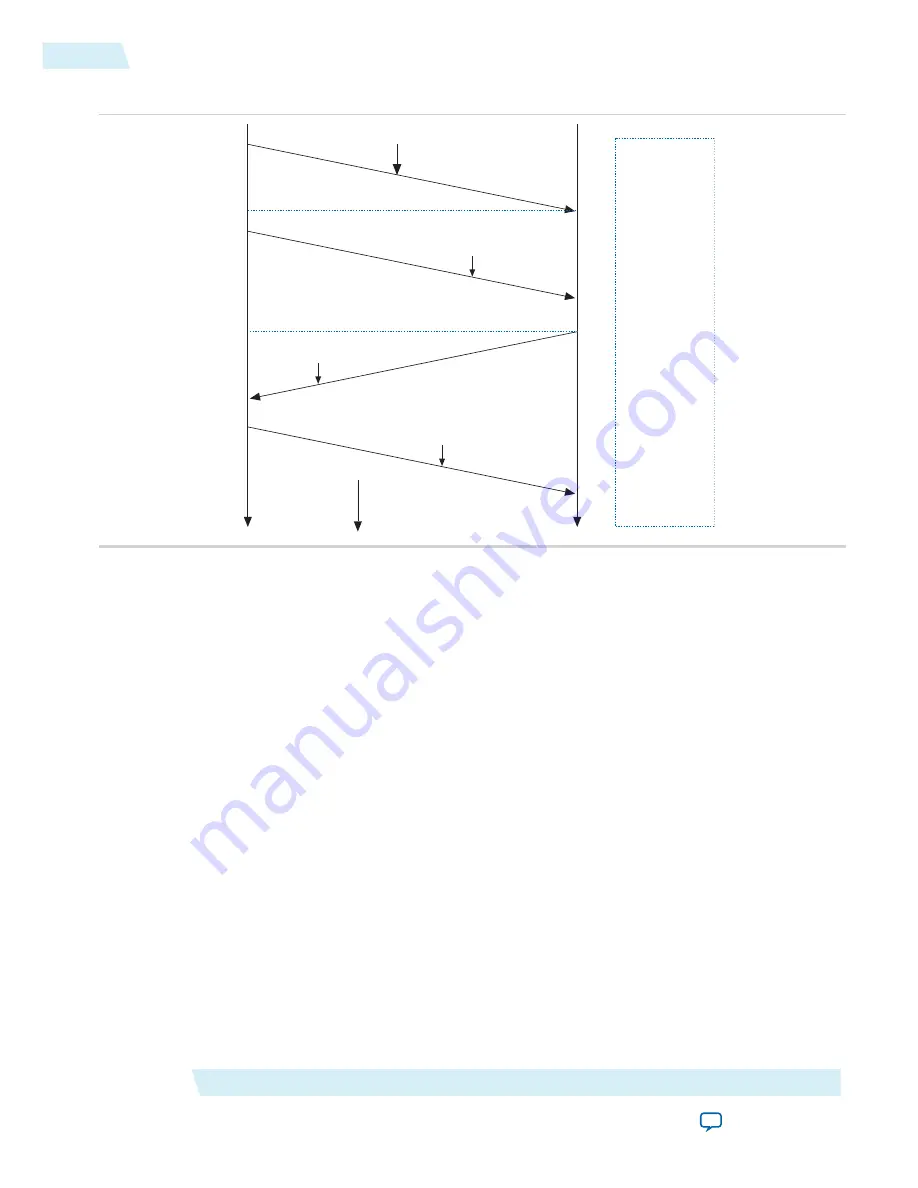

Figure 17-3: Networked Time Synchronization

Master Clock TIme

Slave Clock Time

Time

Delay_Resp Message

Containing t

4

Value

Delay_Req

Message

Follow_Up Message

Containing t

1

Value

Sync Message

t

1

t

2m

t

3m

t

4

t

2

t

3

t

2

t

1

, t

2

t

1

, t

2

, t

3

t

1

, t

2

, t

3

, t

4

Data at

Slave Clock

The PTP uses the following process for synchronizing a slave node to a master node by exchanging the PTP

messages:

1. The master broadcasts the PTP Sync messages to all its nodes. The Sync message contains the master’s

reference time information. The time at which this message leaves the master’s system is t1. This time

must be captured, for Ethernet ports, at the PHY interface.

†

2. The slave receives the sync message and also captures the exact time, t2, using its timing reference.

†

3. The master sends a follow_up message to the slave, which contains t1 information for later use.

†

4. The slave sends a delay_req message to the master, noting the exact time, t3, at which this frame leaves

the PHY interface.

†

5. The master receives the message, capturing the exact time, t4, at which it enters its system.

†

6. The master sends the t4 information to the slave in the delay_resp message.

†

7. The slave uses the four values of t1, t2, t3, and t4 to synchronize its local timing reference to the master’s

timing reference.

†

Most of the PTP implementation is done in the software above the UDP layer. However, the hardware

support is required to capture the exact time when specific PTP packets enter or leave the Ethernet port at

the PHY interface. This timing information must be captured and returned to the software for the proper

implementation of PTP with high accuracy.

†

The EMAC is intended to support IEEE 1588 operation in all modes with a resolution of one. When the two

EMACs are operating in an IEEE 1588 environment, the MPU subsystem is responsible for maintaining

synchronization between the time counters internal to the two MACs.

The IEEE 1588 interface to the FPGA allows the FPGA to provide a source for the emac_ptp_ref_clk input

as well to allow it to monitor the pulse per second output from each EMAC controller.

Ethernet Media Access Controller

Altera Corporation

cv_54017

IEEE 1588-2002 Timestamps

17-12

2013.12.30