MOTOROLA

Chapter 33. Serial Peripheral Interface (SPI)

33-11

Part IV. Communications Processor Module

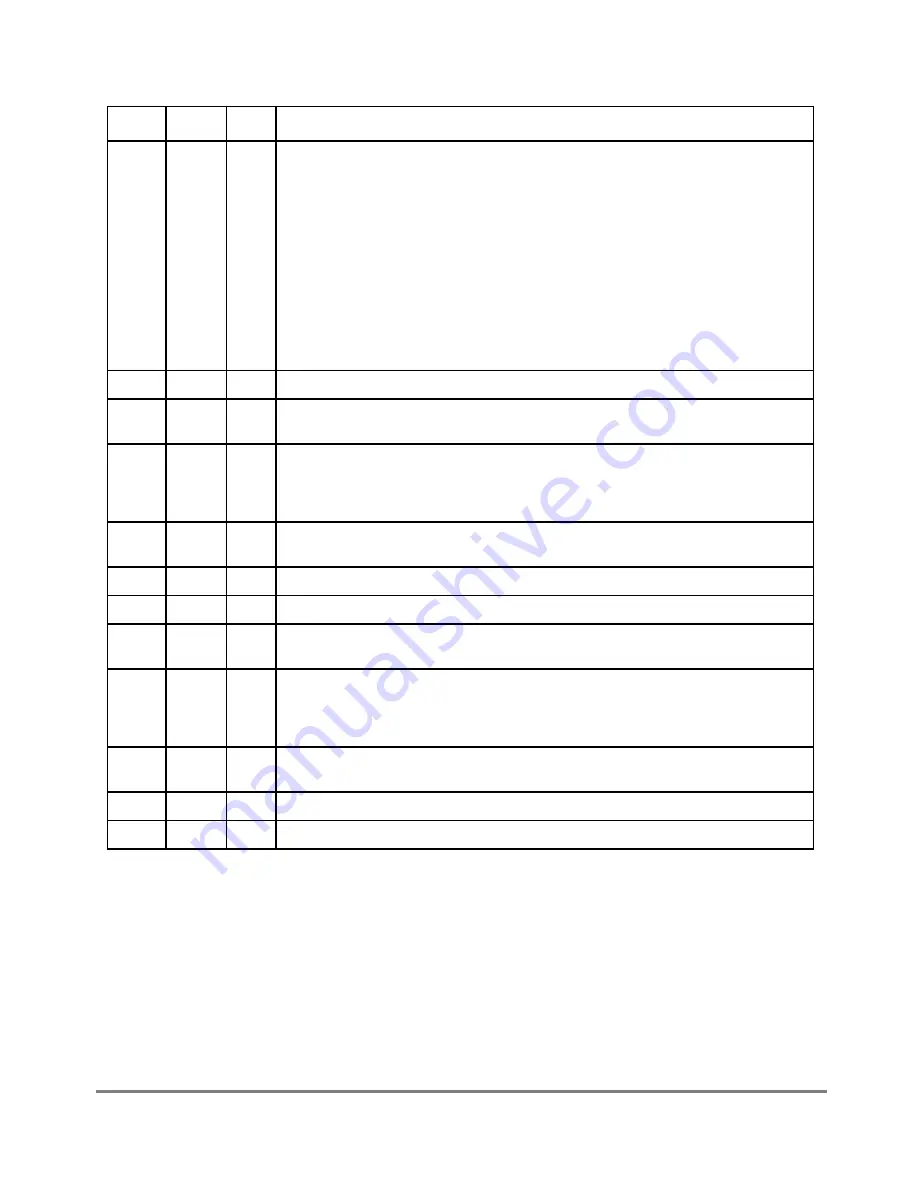

0x06

MRBLR

Hword Maximum receive buffer length. The SPI has one MRBLR entry to deÞne the maximum

number of bytes the MPC8260 writes to a Rx buffer before moving to the next buffer. The

MPC8260 can write fewer bytes than MRBLR if an error or end-of-frame occurs, but

never exceeds the MRBLR value. User-supplied buffers should be no smaller than

MRBLR.

Tx buffers are unaffected by MRBLR and can have varying lengths; the number of bytes

to be sent is programmed in TxBD[Data Length].

MRBLR is not intended to be changed while the SPI is operating. However it can be

changed in a single bus cycle with one 16-bit move (not two 8-bit bus cycles back-to-

back). The change takes effect when the CP moves control to the next RxBD. To

guarantee the exact RxBD on which the change occurs, change MRBLR only while the

SPI receiver is disabled. MRBLR should be greater than zero; it should be an even

number if the character length of the data exceeds 8 bits.

0x08

RSTATE Word

Rx internal state.

2

Reserved for CP use.

0x0C

Ñ

Word

The Rx internal data pointer

2

is updated by the SDMA channels to show the next

address in the buffer to be accessed.

0x10

RBPTR

Hword RxBD pointer. Points to the current Rx BD being processed or to the next BD to be

serviced when idle. After a reset or when the end of the BD table is reached, the CP

initializes RBPTR to the RBASE value. Most applications should not modify RBPTR, but

it can be updated when the receiver is disabled or when no Rx buffer is in use.

0x12

Ñ

Hword The Rx internal byte count

2

is a down-count value that is initialized with the MRBLR

value and decremented with every byte the SDMA channels write.

0x14

Ñ

Word

Rx temp.

2

Reserved for CP use.

0x18

TSTATE Word

Tx internal state.

2

Reserved for CP use.

0x1C

Ñ

Word

The Tx internal data pointer

2

is updated by the SDMA channels to show the next address

in the buffer to be accessed.

0x20

TBPTR

Hword TxBD pointer. Points to the current Tx BD during frame transmission or the next BD to be

processed when idle. After reset or when the end of the Tx BD table is reached, the CP

initializes TBPTR to the TBASE value. Most applications do not need to modify TBPTR,

but it can be updated when the transmitter is disabled or when no Tx buffer is in use.

0x22

Ñ

Hword The Tx internal byte count

2

is a down-count value initialized with TxBD[Data Length] and

decremented with every byte read by the SDMA channels.

0x24

Ñ

Word

Tx temp.

2

Reserved for CP use.

0x34

Ñ

Word

SDMA temp.

1

From the pointer value programmed in SPI_BASE at IMMR + 0x89FC.

2

Normally, these parameters need not be accessed. They are listed to help experienced users in debugging.

Table 33-5. SPI Parameter RAM Memory Map (Continued)

Offset

1

Name

Width

Description

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......