10-66

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

All local bus refreshes are done using the refresh pattern of UPMB. This means that if

refresh is required on the local bus, UPMB must be assigned to the local bus and

MBMR[RFEN] must be set. It also means that only one refresh routine should be

programmed for the local bus, and be placed in UPMB, which serves as the local bus refresh

executor. If refresh is not required on the local bus, UPMB can be assigned to any bus.

UPMC can be assigned to any bus; there is no need to program its refresh routine because

it will use the one in UPMA or UPMB, according to the bus to which it is assigned.

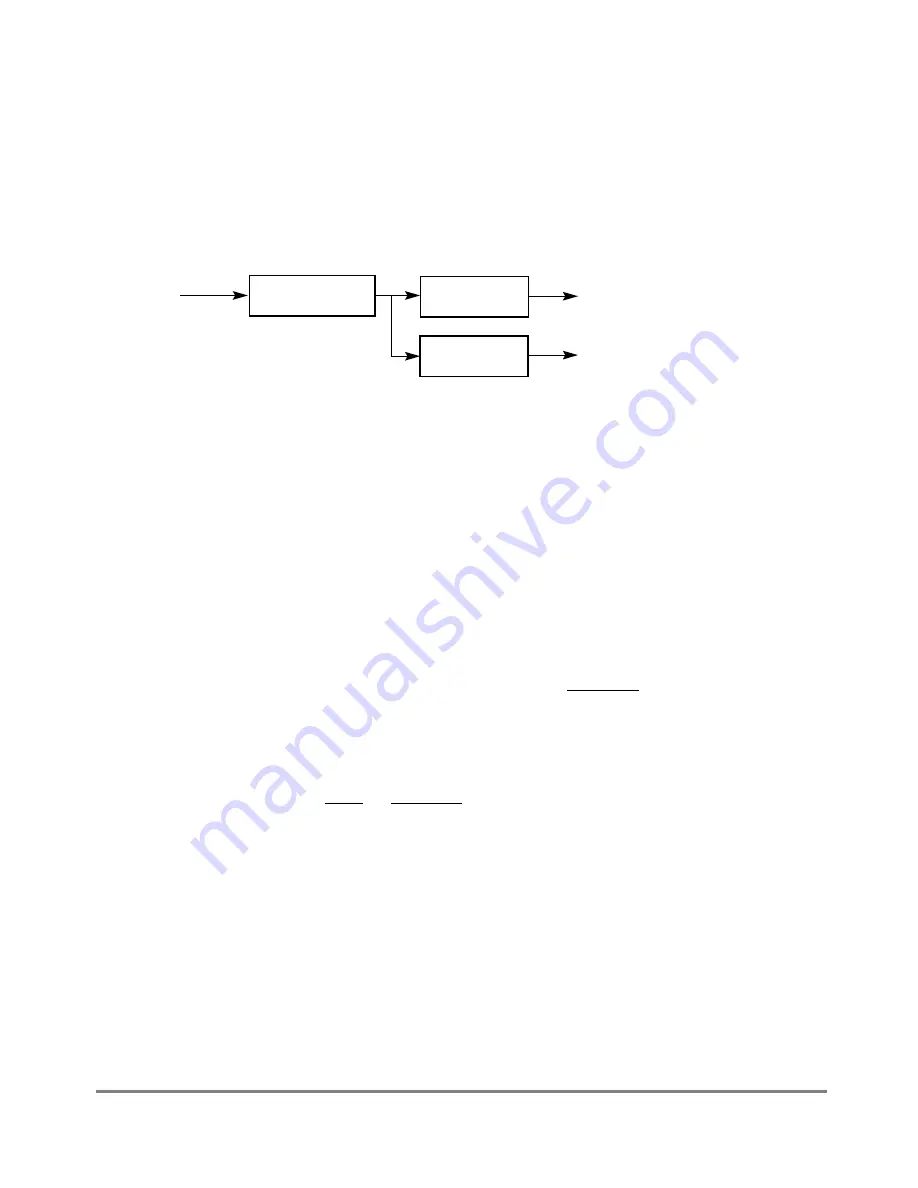

Figure 10-57. Memory Refresh Timer Request Block Diagram

10.6.1.3 Software RequestsÑ

RUN

Command

Software can start a request to the UPM by issuing a

RUN

command to the UPM. Some

memory devices have their own signal handshaking protocol to put them into special

modes, such as self-refresh mode. Other memory devices require special commands to be

issued on their control signals, such as for SDRAM initialization.

For these special cycles, the user creates a special RAM pattern that can be stored in any

unused areas in the UPM RAM. Then the

RUN

command is used to run the cycle. The UPM

runs the pattern beginning at the speciÞed RAM location until it encounters a RAM word

with its LAST bit set. The

RUN

command is issued by setting M

x

MR[OP] = 11 and

accessing the UPMx memory region with a single-byte transaction.

Note that the pattern must contain exactly one assertion of PSDVAL (UTA bit in the RAM

word, described in Table 10-35), otherwise bus timeout may occur.

10.6.1.4 Exception Requests

When the MPC8260 under UPM control initiates an access to a memory device, the

external device may assert TEA or SRESET. The UPM provides a mechanism by which

memory control signals can meet the timing requirements of the device without losing data.

The mechanism is the exception pattern that deÞnes how the UPM deasserts its signals in

a controlled manner.

10.6.2 Programming the UPMs

The UPM is a microsequencer that requires microinstructions or RAM words to generate

signal timings for different memory cycles. Follow these steps to program the UPMs:

1. Set up BR

x

and OR

x

.

2. Write patterns into the RAM array.

60x bus assigned UPM

Local bus assigned UPM

System

Divide by PURT

PTP Prescaling

Divide by LURT

refresh timer request

refresh timer request

Clock

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......