MOTOROLA

Chapter 10. Memory Controller

10-65

Part III. The Hardware Interface

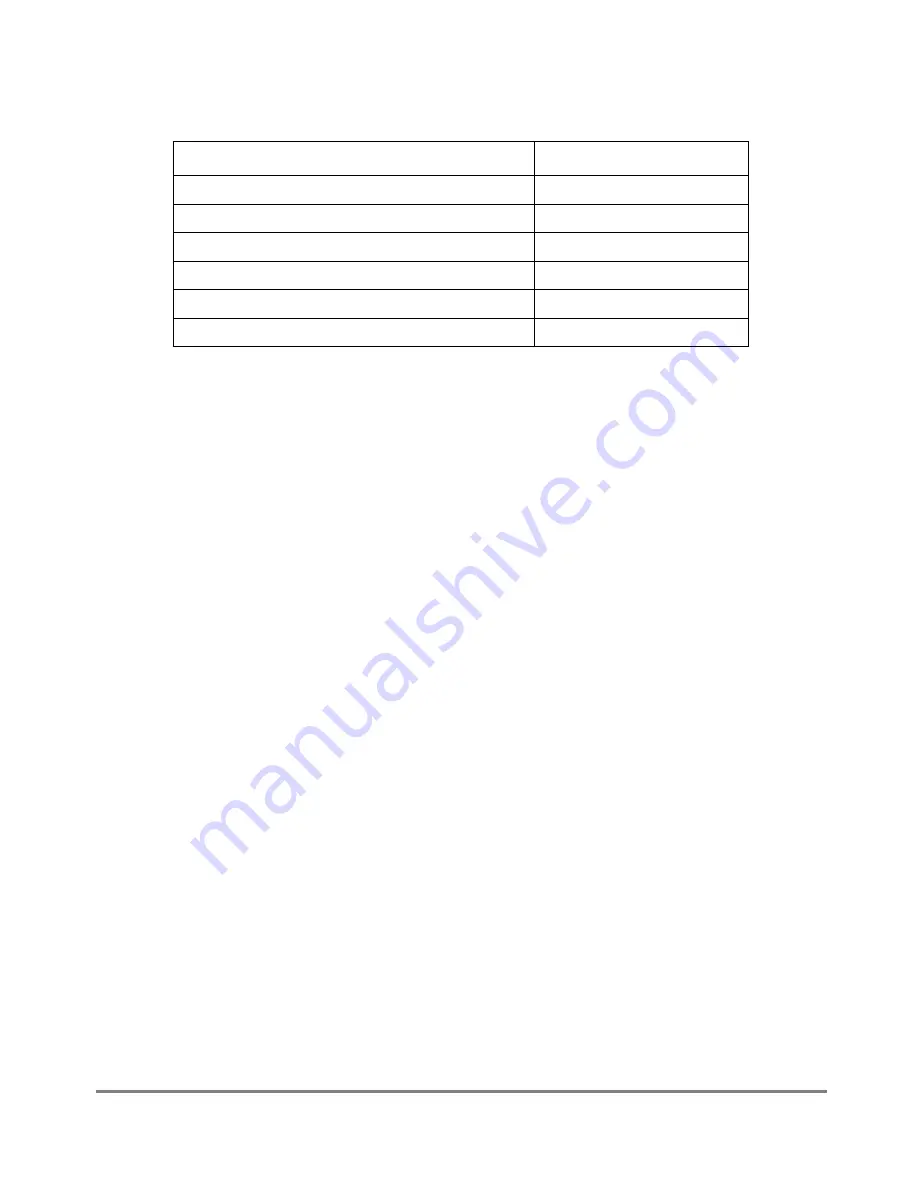

Table 10-34 show the start address of each pattern.

10.6.1.1 Memory Access Requests

When an internal device requests a new access to external memory, the address of transfer

are compared to each valid bank deÞned in BR

x

. The value in BR

x

[MS] selects the UPM

to handle the memory access. The user must ensure that the UPM is appropriately

initialized before a request.

The UPM supports two types of memory reads and writes:

¥

A single-beat transfer transfers one operand consisting of up to double word. A

single-beat cycle starts with one transfer start and ends with one transfer

acknowledge.

¥

A burst transfer transfers four double words. For 64-bit accesses, the burst cycle

starts with one transfer start but ends after four transfer acknowledges. A 32-bit

device requires 8 data acknowledges; an 8-bit device requires 32. See

Section 10.2.13, ÒPartial Data Valid Indication (PSDVAL).Ó

The MPC8260 deÞnes two additional transfer sizes: bursts of two and three doublewords.

These access are treated by the UPM as back-to-back, single-beat transfers.

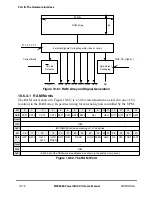

10.6.1.2 UPM Refresh Timer Requests

Each UPM contains a refresh timer that can be programmed to generate refresh service

requests of a particular pattern in the RAM array. Figure 10-57 shows the hardware

associated with memory refresh timer request generation. PURT deÞnes the period for the

timers associated with UPM

x

on the 60x bus and LURT deÞnes it on the local bus. See

Section 10.3.8, Ò60x Bus-Assigned UPM Refresh Timer (PURT),Ó and Section 10.3.9,

ÒLocal Bus-Assigned UPM Refresh Timer (LURT).Ó

All 60x bus refreshes are done using the refresh pattern of UPMA. This means that if

refresh is required on the 60x bus, UPMA must be assigned to the 60x bus and

M

x

MR[RFEN] must be set. It also means that only one refresh routine should be

programmed for the 60x bus and be placed in UPMA, which serves as the 60x bus refresh

executor. If refresh is not required on the 60x bus, UPMA can be assigned to any bus.

Table 10-34. UPM Routines Start Addresses

UPM Routine

Routine Start Address

Read single-beat (RSS)

0x00

Read burst (RBS)

0x08

Write single-beat (WSS)

0x18

Write burst (WBS)

0x20

Refresh timer (PTS)

0x30

Exception condition (EXS)

0x3C

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......