29-64

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

Table 29-31 describes control slot Þelds.

29.10.5 ATM Controller Buffer Descriptors (BDs)

Each ATM channel has separate receive and transmit BD tables. The number of BDs per

channel and the size of the buffers is user-deÞned. The last BD in each table holds a wrap

indication. Each BD in the TxBD table points to a buffer to send. At the receive side, the

user can choose one of two modes:

¥

Static buffer allocation. In this mode, the user allocates dedicated buffers to each

ATM channel (that is, the user associates each BD with one buffer). Static buffer

allocation is useful when the connection rate is known and constant and when data

must be reassembled in a particular memory space.

¥

Global buffer allocation. Available for AAL5 only. In this mode, buffer allocation is

dynamic. The user allocates receive buffers and places them in global buffer pools.

When the CP needs a receive buffer, it Þrst fetches a buffer pointer from one of the

global buffer pools and writes the pointer to the current RxBD. Global buffer

allocation is optimized for allocating memory among many ATM channels with

variable data rates, such as ABR channels.

29.10.5.1 Transmit Buffer Operations

The user prepares a table of BDs pointing to the buffers to be sent. The address of the Þrst

BD is put in the channelÕs TCT[TBD_BASE]. The transmit process starts when the core

issues an

ATM

TRANSMIT

command. The CP reads the Þrst TxBD in the table and sends its

associated buffer. When the current buffer is Þnished, the CP increments TBD_Offset,

which holds the offset from TBD_BASE to the current BD. It then reads the next BD in the

table. If the BD is ready (TxBD[R] = 1), the CP continues sending. If the current BD is not

ready, the CP polls the ready bit at the channel rate unless TCT[AVCF] = 1, in which case

the CP removes the channel from the APC and clears TCT[VCON]. The core must issue a

new

ATM

TRANSMIT

command to restart transmission.

Figure 29-41 shows the ready bit in the TxBD tables and their associated buffers for two

example ATM channels.

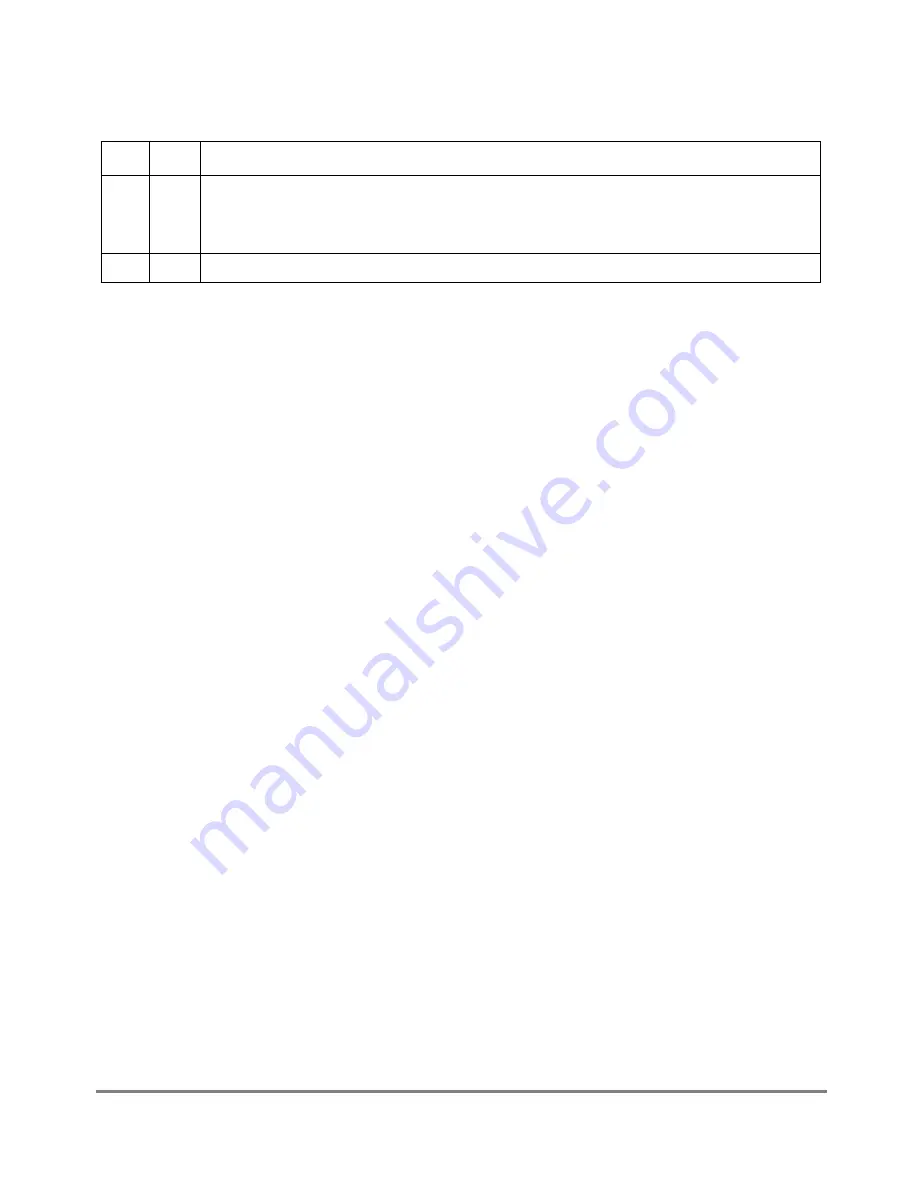

Table 29-31. Control Slot Field Description

Bits

Name

Description

0

TCTE

Used for external channels only.

0 Channels in this scheduling table do not use external TCTE. (No external VBR, ABR, UBR+

channels)

1 Channels in this scheduling table use external TCTE. (External VBR, ABR, UBR+ channels)

1Ð15

Ñ

Reserved, should be cleared.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......