MOTOROLA

Chapter 30. Fast Ethernet Controller

30-9

Part IV. Communications Processor Module

30.8 Ethernet Parameter RAM

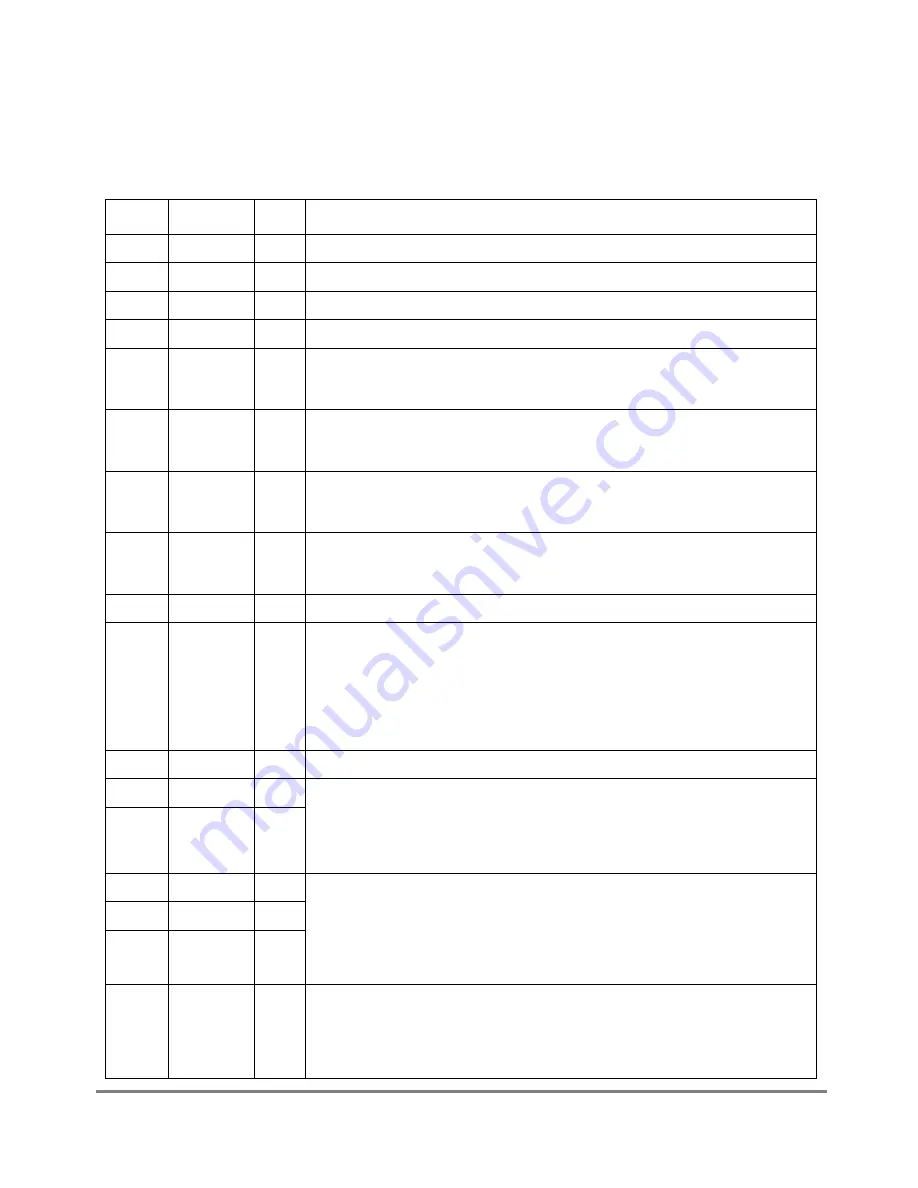

For Ethernet mode, the protocol-speciÞc area of the FCC parameter RAM is mapped as in

Table 30-2.

Table 30-2. Ethernet-Specific Parameter RAM

Offset

1

Name

Width

Description

0x3C

STAT_BUF

Word

Buffer of internal usage

0x40

CAM_PTR

Word

CAM address

0x44

C_MASK

Word

Constant MASK for CRC (initialize to 0xDEBB_20E3). For the 32-bit CRC-CCITT.

0x48

C_PRES

Word

Preset CRC (initialize to 0xFFFF_FFFF). For the 32-bit CRC-CCITT.

0x4C

CRCEC

2

Word

CRC error counter. Counts each received frame with a CRC error. Does not count

frames not addressed to the station, frames received in the out-of-buffers condition,

frames with overrun errors, or frames with alignment errors.

0x50

ALEC

2

Word

Alignment error counter. Counts frames received with dribbling bits. Does not count

frames not addressed to the station, frames received in the out-of-buffers condition,

or frames with overrun errors.

0x54

DISFC

2

Word

Discard frame counter. Incremented for discarded frames because of an out-of-

buffers condition or overrun error. The CRC need not be correct for this counter to be

incremented.

0x58

RET_LIM

Hword Retry limit (typically 15 decimal). Number of retries that should be made to send a

frame. If the frame is not sent after this limit is reached, an interrupt can be

generated.

0x5A

RET_CNT

Hword Retry limit counter. Temporary decrementer used to count retries made.

0x5C

P_PER

Hword Persistence. Allows the Ethernet controller to be less persistent after a collision.

Normally cleared, P_PER can be from 0 to 9 (9 = least persistent). The value is

added to the retry count in the backoff algorithm to reduce the chance of

transmission on the next time-slot. Using a less persistent backoff algorithm

increases throughput in a congested Ethernet LAN by reducing the chance of

collisions. FPSMR[SBT] can also reduce persistence of the Ethernet controller. The

Ethernet/802.3 speciÞcations permit the use of P_PER.

0x5E

BOFF_CNT

Hword Backoff counter

0x60

GADDR_H

Word

Group address Þlters high and low are used in the hash table function of the group

addressing mode. The user may write zeros to these values after reset and before

the Ethernet channel is enabled to disable all group hash address recognition

functions. The

SET

GROUP

ADDRESS

command is used to enable the hash table. See

Section 30.13, ÒHash Table Algorithm.Ó

0x64

GADDR_L

Word

0x68

TFCSTAT

Hword Out-of-sequence TxBD. Includes the status/control, data length, and buffer pointer

Þelds in the same format as a regular TxBD. Useful for sending ßow control frames.

This areaÕs TxBD[R] is always checked between frames, regardless of

FPSMR

x

[FCE]. If it is not ready, a regular frame is sent. The user must set TxBD[L]

when preparing this BD. If TxBD[I] is set, a TXC event is generated after frame

transmission. This area should be cleared when not in use.

0x6A

TFCLEN

Hword

0x6C

TFCPTR

Word

0x70

MFLR

Hword Maximum frame length register (typically1518 decimal). If the Ethernet controller

detects an incoming frame exceeding MFLR, it sets RxBD[LG] (frame too long) in the

last RxBD, but does not discard the rest of the frame. The controller also reports the

frame status and length of the received frame in the last RxBD. MFLR includes all in-

frame bytes between the start frame delimiter and the end of the frame.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......