20-4

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

receive shift register are transferred to the receive FIFO before proceeding to the receive

buffer. The CPM ßags UART events, including reception errors, in SCCE and the RxBD

status and control Þelds. GSMR_H[RFW] must be set for an 8-bit receive FIFO.

The synchronous UART transmit shift register sends outgoing data on TXD

x

. Data is then

clocked synchronously with the transmit clock, which can have an internal or external

source.

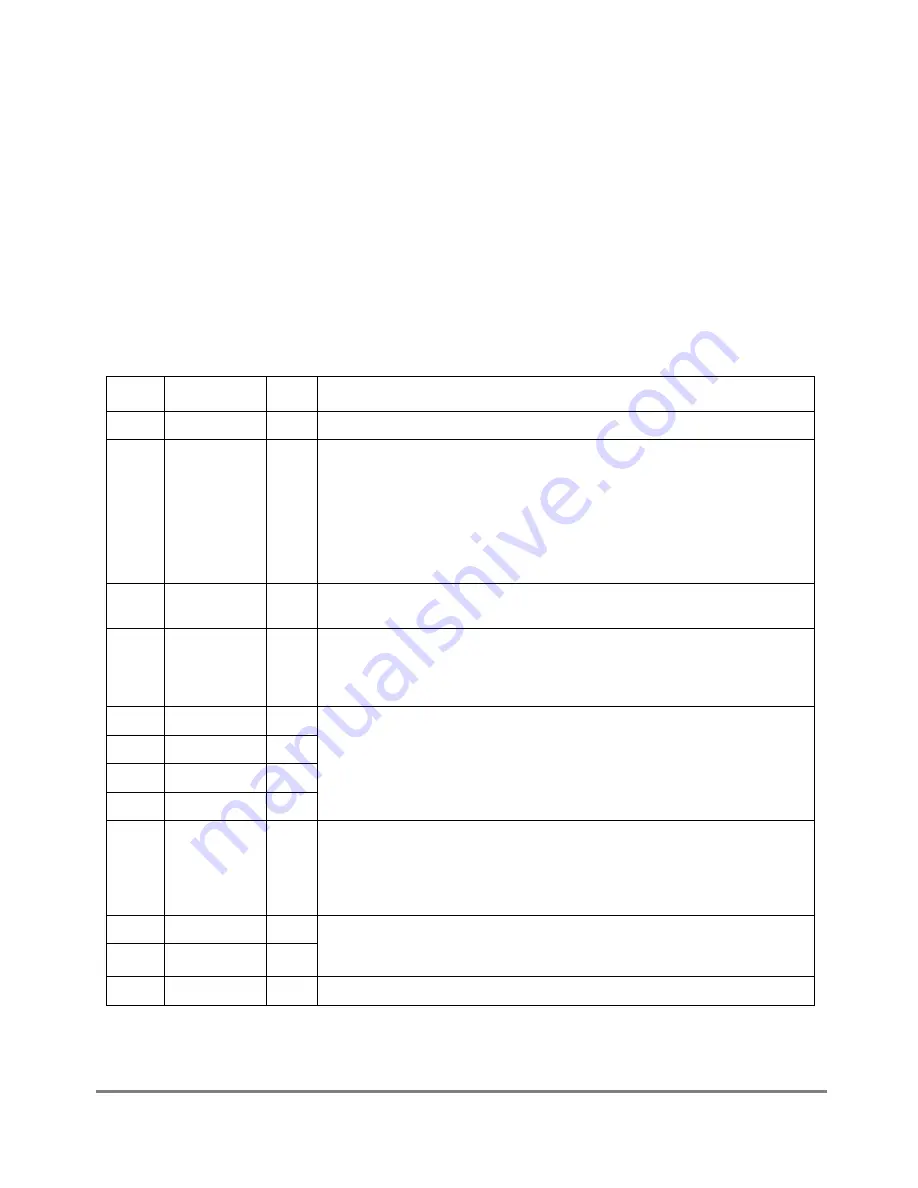

20.4 SCC UART Parameter RAM

For UART mode, the protocol-speciÞc area of the SCC parameter RAM is mapped as in

Table 20-1.

Table 20-1. UART-Specific SCC Parameter RAM Memory Map

Offset

1

Name

Width

Description

0x30

Ñ

DWord Reserved

0x38

MAX_IDL

Hword Maximum idle characters. When a character is received, the receiver begins

counting idle characters. If MAX_IDL idle characters are received before the next

data character, an idle timeout occurs and the buffer is closed, generating a

maskable interrupt request to the core to receive the data from the buffer. Thus,

MAX_IDL offers a way to demarcate frames. To disable the feature, clear

MAX_IDL. The bit length of an idle character is calculated as follows: 1 + data

length (5Ð9) + 1 (if parity is used) + number of stop bits (1Ð2). For 8 data bits, no

parity, and 1 stop bit, the character length is 10 bits.

0x3A

IDLC

Hword Temporary idle counter. Holds the current idle count for the idle timeout process.

IDLC is a down-counter and does not need to be initialized or accessed.

0x3C

BRKCR

Hword Break count register (transmit). Determines the number of break characters the

transmitter sends. The transmitter sends a break character sequence when a

STOP

TRANSMIT

command is issued. For 8 data bits, no parity, 1 stop bit, and 1 start bit,

each break character consists of 10 zero bits.

0x3E

PAREC

Hword User-initialized,16-bit (moduloÐ2

16

) counters incremented by the CP.

PAREC counts received parity errors.

FRMEC counts received characters with framing errors.

NOSEC counts received characters with noise errors.

BRKEC counts break conditions on the signal. A break condition can last for

hundreds of bit times, yet BRKEC is incremented only once during that period.

0x40

FRMEC

Hword

0x42

NOSEC

Hword

0x44

BRKEC

Hword

0x46

BRKLN

Hword Last received break length. Holds the length of the last received break character

sequence measured in character units. For example, if RXD

x

is low for 20 bit times

and the deÞned character length is 10 bits, BRKLN = 0x002, indicating that the

break sequence is at least 2 characters long. BRKLN is accurate to within one

character length.

0x48

UADDR1

Hword UART address character 1/2. In multidrop mode, the receiver provides automatic

address recognition for two addresses. In this case, program the lower order bytes

of UADDR1 and UADDR2 with the two preferred addresses.

0x4A

UADDR2

Hword

0x4C

RTEMP

Hword Temp storage

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......