28-10

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

The BDs and data buffers can be anywhere in the system memory.

The CP processes the TxBDs in a straightforward fashion. Once the transmit side of an FCC

is enabled, it starts with the Þrst BD in that FCCÕs TxBD table. When the CP detects that

TxBD[R] is set, it begins processing the buffer. The CP detects that the BD is ready either

by polling the R bit periodically or by the user writing to the TODR. When the data from

the BD has been placed in the transmit FIFO buffer, the CP moves on to the next BD, again

waiting for the R bit to be set. Thus, the CP does no look-ahead BD processing, nor does it

skip over BDs that are not ready. When the CP sees the wrap (W) bit set in a BD, it goes

back to the beginning of the BD table after processing of the BD is complete.

After using a BD, the CP normally clears R (not-ready); thus, the CP does not use a BD

again until the BD has been prepared by the core. Some protocols support continuous

mode, which allows repeated transmission and for which the R bit remains set (always

ready).

The CP uses RxBDs in a similar fashion. Once the receive side of an FCC is enabled, it

starts with the Þrst BD in the FCCÕs RxBD table. Once data arrives from the serial line into

the FCC, the CP performs the required protocol processing on the data and moves the

resultant data to the buffer pointed to by the Þrst BD. Use of a BD is complete when no

room is left in the buffer or when certain events occur, such as the detection of an error or

end-of-frame. Regardless of the reason, the buffer is then said to be closed and additional

data is stored using the next BD. Whenever the CP needs to begin using a BD because new

data is arriving, it checks the E bit of that BD. This check is made on a prefetched copy of

the current BD. If the current BD is not empty, it reports a busy error. However, it does not

move from the current BD until it is empty. Because there is a periodic prefetch of the

RxBD, the busy error may recur if the BD is not prepared soon enough.

When the CP sees the W bit set in a BD, it returns to the beginning of the BD table after

processing of the BD is complete. After using a BD, the CP clears the E bit (not empty) and

does not use a BD again until the BD has been processed by the core. However, in

continuous mode, available to some protocols, the E bit remains set (always empty).

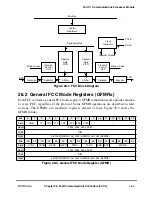

28.7 FCC Parameter RAM

Each FCC parameter RAM area begins at the same offset from each FCC base area. The

protocol-speciÞc portions of the FCC parameter RAM are discussed in the speciÞc protocol

descriptions. Table 28-5 shows portions common to all FCC protocols.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......