MOTOROLA

Chapter 27. Multi-Channel Controllers (MCCs)

27-23

Part IV. Communications Processor Module

The data length and buffer pointer are described as follows:

¥

Data length. Data length is the number of octets written by the CP into this BDÕs data

buffer. It is written by the CP when the BD is closed. When this is the last BD in the

frame (L = 1), the data length contains the total number of frame octets (including

two or four bytes for CRC). Note that memory allocated for buffers should be not

smaller than the contents of the maximum receive buffer length register (MRBLR).

The data length does not include the time stamp.

¥

Rx buffer pointer. The receive buffer pointer points to the Þrst location of the

associated data buffer. This value must be equal to 8*

n

if CHAMR[TS] = 0 and equal

to 8*

n

- 4 if CHAMR[TS] = 1 (where

n

is any integer larger than 0).

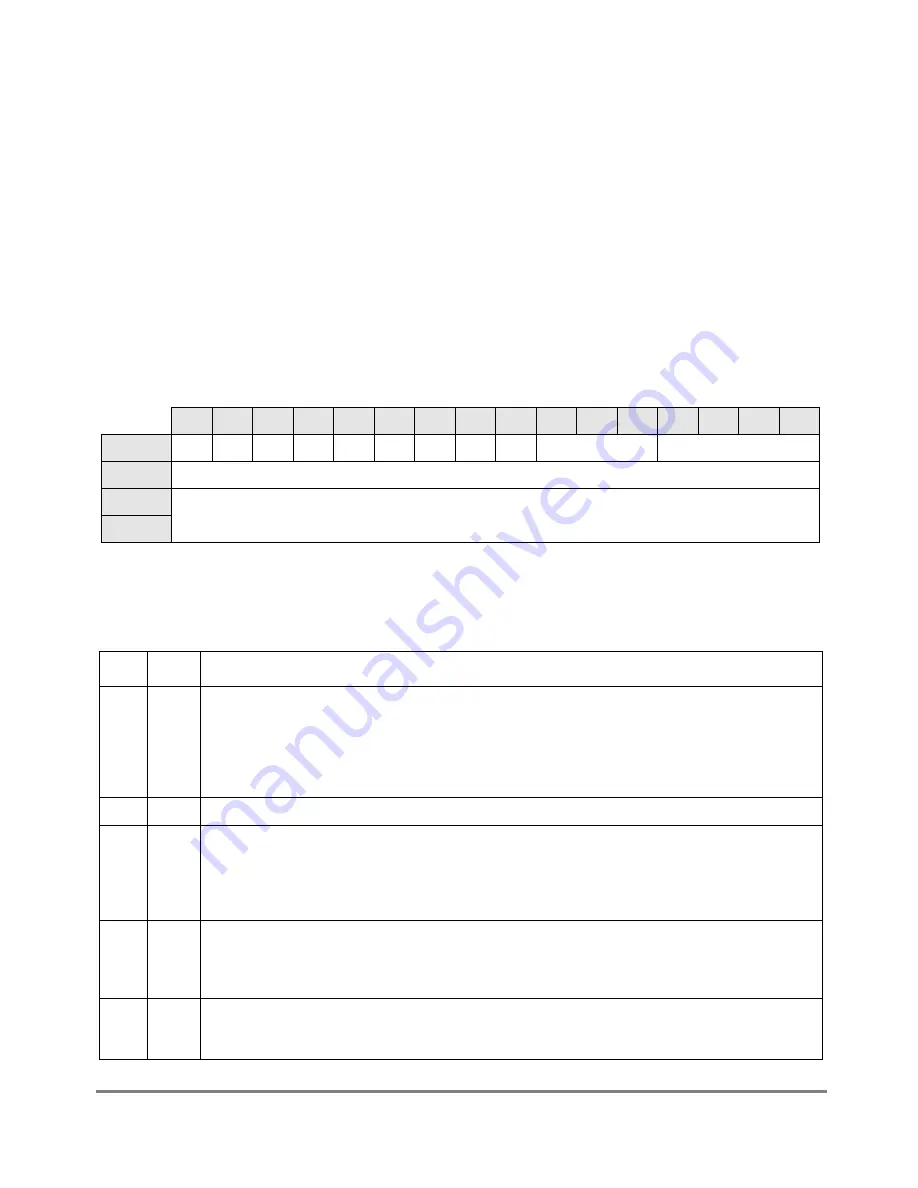

27.11.2 Transmit Buffer Descriptor (TxBD)

Figure 27-16 shows the TxBD.

Table 27-16 describes TxBD Þelds.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

R

Ñ

W

I

L

TC

CM

Ñ

UB

Ñ

PAD

2

Data Length

4

Tx Data Buffer Pointer

6

Figure 27-16. MCC Transmit Buffer Descriptor (TxBD)

Table 27-16. TxBD Field Descriptions

Bits

Name

Description

0

R

Ready

0 The buffer associated with this BD is not ready for transmission. The user is free to manipulate this

BD or its associated data buffer. The CP clears this bit after the buffer has been transmitted or after

an error condition is encountered.

1 The data buffer is ready to be transmitted. The transmission may have begun, but it has not

completed. The user cannot modify this BD once this bit is set.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (Þnal BD in table)

0 This is not the last BD in the TxBD table.

1 This is the last BD in the TxBD table. After this buffer is used, the CP receives incoming data into the

Þrst BD in the table (the BD pointed to by TBASE). The number of TxBDs in this table is

programmable and is determined the wrap bit.

3

I

Interrupt

0 No interrupt is generated after this buffer has been serviced.

1 TXB in the circular interrupt table entry is set when this buffer has been serviced by the MCC. This

bit can cause an interrupt (if enabled).

4

L

Last

0 This is not the last buffer in the frame.

1 This is the last buffer in the current frame.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......