MOTOROLA

Chapter 2. PowerPC Processor Core

2-13

Part I. Overview

11

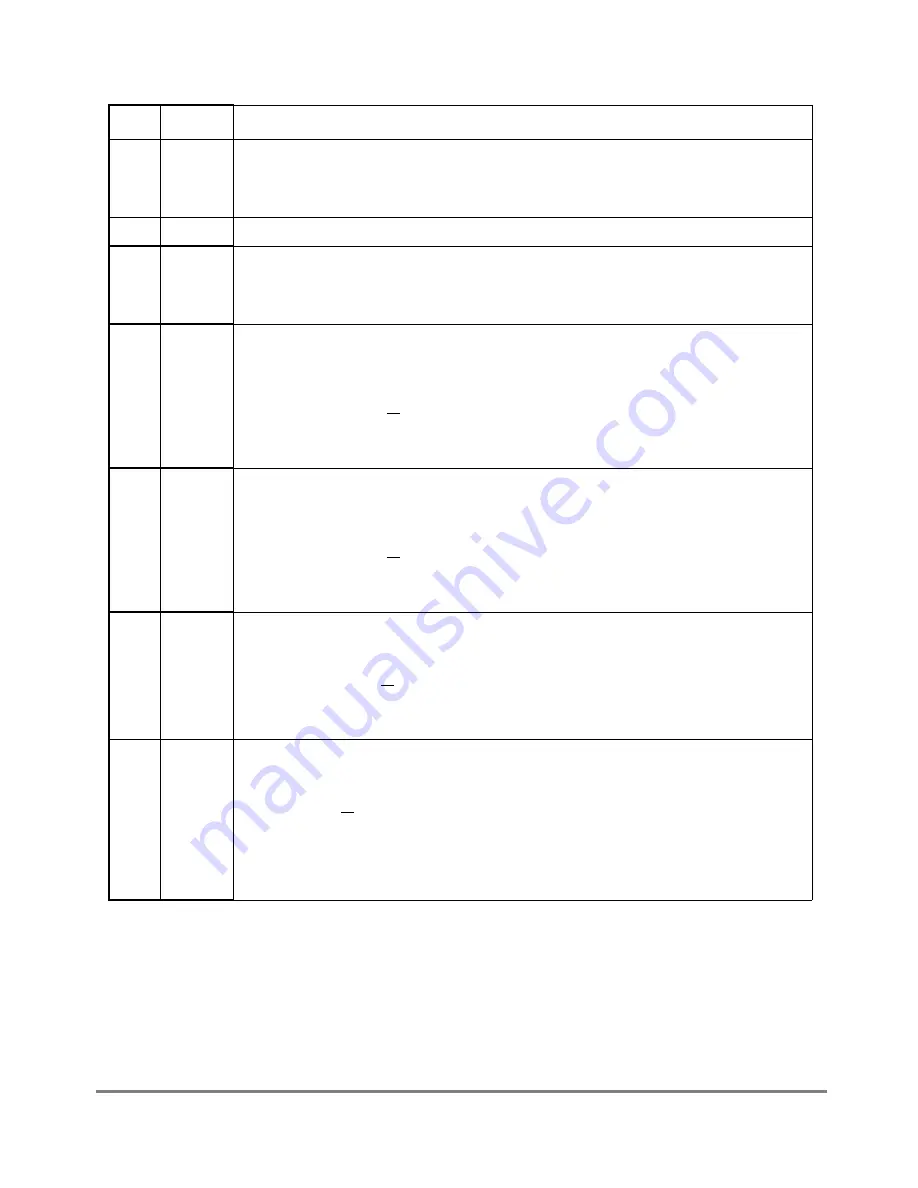

DPM

Dynamic power management enable.

1

0 Dynamic power management is disabled.

1 Functional units enter a low-power mode automatically if the unit is idle. This does not affect

operational performance and is transparent to software or any external hardware.

12Ð14

Ñ

Reserved

15

NHR

Not hard reset (software-use only)ÑHelps software distinguish a hard reset from a soft reset.

0 A hard reset occurred if software had previously set this bit.

1 A hard reset has not occurred. If software sets this bit after a hard reset, when a reset occurs

and this bit remains set, software can tell it was a soft reset.

16

ICE

Instruction cache enable

2

0 The instruction cache is neither accessed nor updated. All pages are accessed as if they were

marked cache-inhibited (WIM = X1X). Potential cache accesses from the bus (snoop and

cache operations) are ignored. In the disabled state for the L1 caches, the cache tag state bits

are ignored and all accesses are propagated to the bus as single-beat transactions. For those

transactions, however, CI reßects the original state determined by address translation

regardless of cache disabled status. ICE is zero at power-up.

1 The instruction cache is enabled

17

DCE

Data cache enable

2

0 The data cache is neither accessed nor updated. All pages are accessed as if they were

marked cache-inhibited (WIM = X1X). Potential cache accesses from the bus (snoop and

cache operations) are ignored. In the disabled state for the L1 caches, the cache tag state bits

are ignored and all accesses are propagated to the bus as single-beat transactions. For those

transactions, however, CI reßects the original state determined by address translation

regardless of cache disabled status. DCE is zero at power-up.

1 The data cache is enabled.

18

ILOCK

Instruction cache lock

0 Normal operation

1 Instruction cache is locked. A locked cache supplies data normally on a hit, but an access is

treated as a cache-inhibited transaction on a miss. On a miss, the transaction to the bus is

single-beat, however, CI still reßects the original state as determined by address translation

independent of cache locked or disabled status.

To prevent locking during a cache access, an

isync

must precede the setting of ILOCK.

19

DLOCK

Data cache lock

0 Normal operation

1 Data cache is locked. A locked cache supplies data normally on a hit but an access is treated

as a cache-inhibited transaction on a miss. On a miss, the transaction to the bus is single-

beat, however, CI still reßects the original state as determined by address translation

independent of cache locked or disabled status. A snoop hit to a locked L1 data cache

performs as if the cache were not locked. A cache block invalidated by a snoop remains invalid

until the cache is unlocked.

To prevent locking during a cache access, a

sync

must precede the setting of DLOCK.

Table 2-1. HID0 Field Descriptions (Continued)

Bits

Name

Description

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......