8-14

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

Note that the basic coherency size of the bus is 32 bytes for the processor (cache-block

size). Data transfers that cross an aligned 32-byte boundary must present a new address

onto the bus at that boundary for proper snoop operation, or must operate as non-coherent

with respect to the MPC8260.

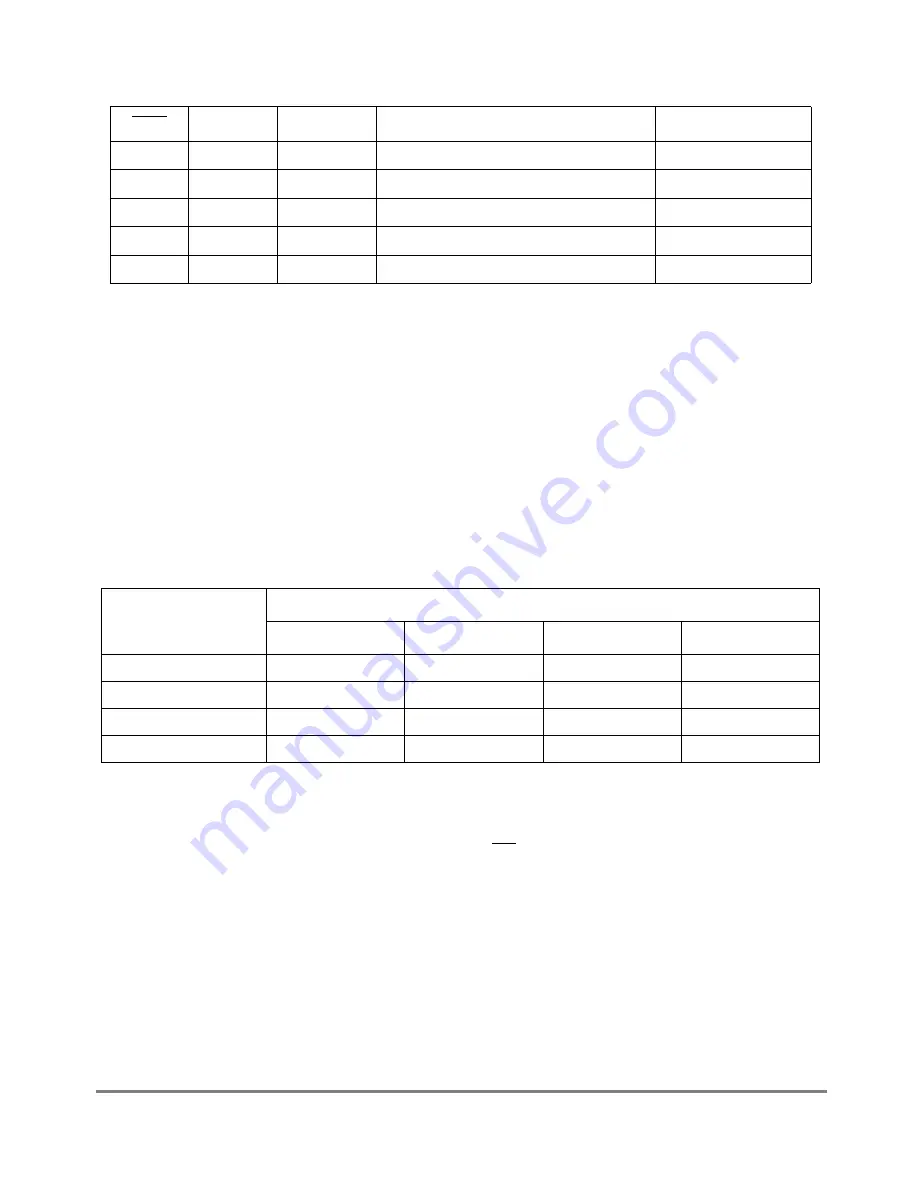

8.4.3.4 Burst Ordering During Data Transfers

During burst transfers, 32 bytes of data (one cache block) are transferred to or from the

cache. Burst write transfers are performed zero double-word-Þrst. However, because burst

reads are performed critical-double-word-Þrst, a burst-read transfer may not start with the

Þrst double word of the cache block and the cache-block-Þll operation may wrap around

the end of the cache block. Table 8-5 describes MPC8260 burst ordering.

Each data beat is terminated with an assertion of TA.

8.4.3.5 Effect of Alignment on Data Transfers

Table 8-6 lists the aligned transfers that can occur to and from the MPC8260. These are

transfers in which the data is aligned to an address that is an integer multiple of the size of

the data. For example, Table 8-6 shows that 1-byte data is always aligned; however, a 4-byte

word must reside at an address that is a multiple of 4 to be aligned.

In Figure 8-6, Table 8-8, and Table 8-9, OP0 is the most-signiÞcant byte of a word operand

and OP7 is the least-signiÞcant byte.

Negated

0 1 1 1

7 Bytes

Extended 7 bytes

SDMA (MPC8260 only)

Negated

0 0 0 0

8 Bytes

Double-word (maximum data bus size)

Core and DMA

Negated

1 0 0 1

16 Bytes

Extended double double-word

SDMA (MPC8260 only)

Negated

1 0 1 0

24 Bytes

Extended triple double-word

SDMA (MPC8260 only)

Asserted

0 0 1 0

32 bytes

Quad double-word (4 maximum data beats)

Core and DMA

Table 8-5. Burst Ordering

Data Transfer

Double-Word Starting Address:

A[27Ð28] = 00

1

1

A[27Ð28] speciÞes the Þrst double word of the 32-byte block being transferred; any subsequent double words must

wrap-around the block. A[29Ð31] are always 0b000 for burst transfers by the MPC8260.

A[27Ð28] = 01

A[27Ð28] = 10

A[27Ð28] = 11

1st data beat

DW0

2

2

DW

x

represents the double word that would be addressed by A[27Ð28] =

x

if a nonburst transfer were performed.

DW1

DW2

DW3

2nd data beat

DW1

DW2

DW3

DW0

3rd data beat

DW2

DW3

DW0

DW1

4th data beat

DW3

DW0

DW1

DW2

Table 8-4. Transfer Size Signal Encoding (Continued)

TBST

TSIZ[0Ð3]

Transfer Size

Comments

Source

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......