6-6

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

WT

BADDR30

IRQ3

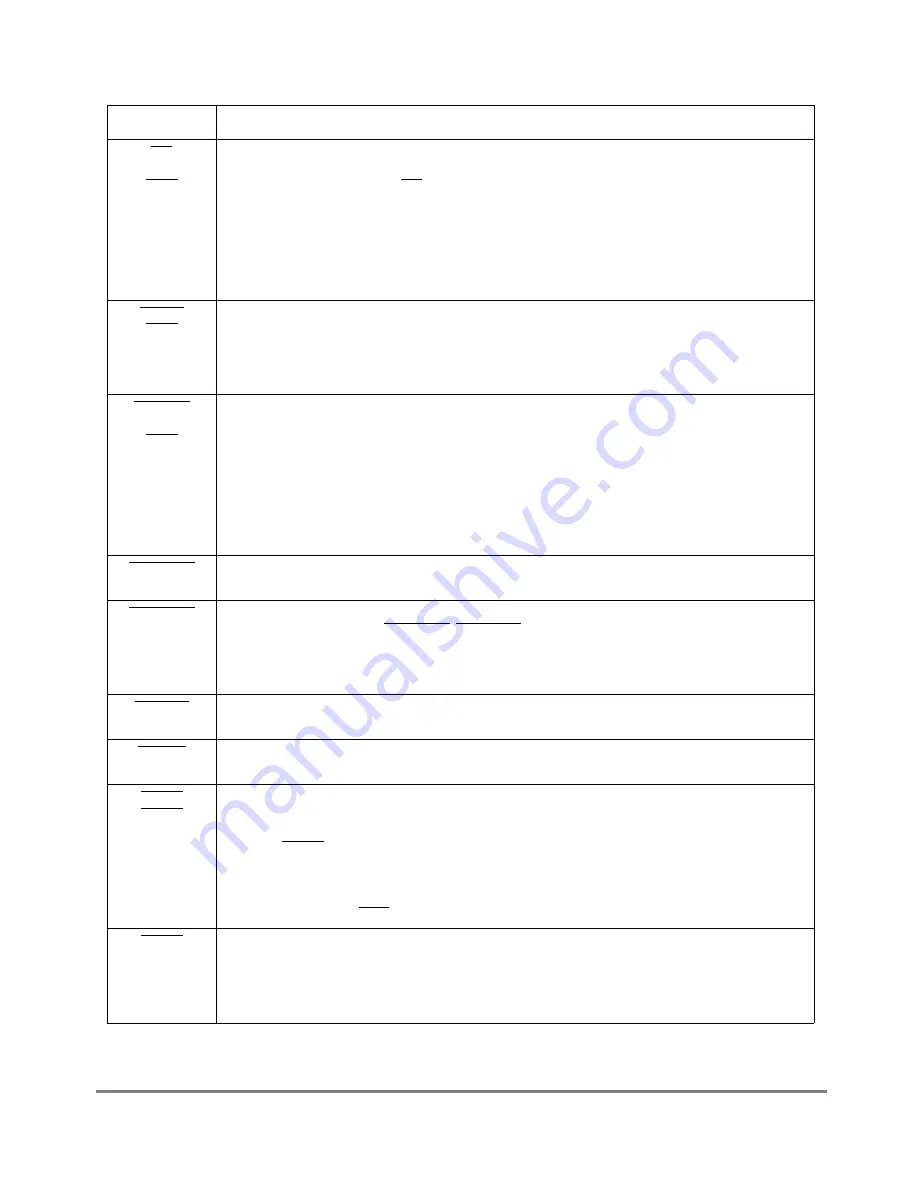

Write throughÑOutput used for L2 cache control. For each core-initiated MPC8260 60x

transaction, the state of this pin indicates if the transaction should be cached using write-through or

copy-back mode. Assertion of WT indicates that the transaction should be cached using the

write-through mode.

Burst address 30ÑThere are Þve burst address output pins. These pins are outputs of the 60x

memory controller. These pins are used in external master conÞguration and are connected directly

to memory devices controlled by MPC8260Õs memory controller.

Interrupt request 3ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

L2_HIT

IRQ4

L2 cache hitÑ(Input). It is used for L2 cache control. Assertion of this pin indicates that the 60x

transaction will be handled by the L2 cache. In this case, the memory controller will not start an

access to the memory it controls.

Interrupt request 4ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

CPU_BG

BADDR31

IRQ5

CPU bus grantÑ(Output) The value of the 60x core bus grant is driven on this pin for the use of an

external MPC2605GA L2 cache. The driven bus grant is non qualiÞed, that is, in case of external

arbiter the user should qualify this signal with the bus grant input to the MPC8260 before

connecting it to the L2 cache.

Burst address 31ÑThere are Þve burst address output of the 60x memory controller used in

external master conÞguration and are connected directly to the memory devices controlled by

MPC8260Õs memory controller.

Interrupt Request 5ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

CPU_DBG

CPU bus data bus grantÑ(Output) The value of the 60x core data bus grant is driven on this pin for

the use of an external MPC2605GA L2 cache.

CPU_DBG

CPU data bus grantÑ(Output). The OR of all data bus grant signals for internal masters from the

internal arbiter is driven on CPU_DBG. CPU_DBG should be connected to the CPU_DBG input of

an external MPC2605GA L2 cache if the internal arbiter is used (BCR[EARB] = 0). If an external

arbiter is used in this MPC8260, the CPU_DBG input of the L2 cache should be connected to the

DBG driven from the external arbiter to this MPC8260.

CPU_BR

CPU bus requestÑ(Output) The value of the 60x core bus request is driven on this pin for the use

of an external MPC2605GA L2 cache.

CS[0Ð9]

Chip selectÑThese are output pins that enable speciÞc memory devices or peripherals connected

to MPC8260 buses.

CS[10]

BCTL1

DBG_DIS

Chip selectÑThese are output pins that enable speciÞc memory devices or peripherals connected

to MPC8260 buses.

Buffer control 1ÑOutput signal whose its function is controlling buffers on the 60x data bus. Usually

used with BCTL0. The exact function of this pin is deÞned by the value of SIUMCR[BCTLC]. See

Section 4.3.2.6, ÒSIU Module ConÞguration Register (SIUMCR),Ó for details.

Data bus grant disableÑThis is an output when the MPC8260 is in external arbiter mode and an

input when the MPC8260 is in internal arbiter mode. When this pin is asserted, the 60x bus arbiter

should negate all of its DBG outputs to prevent data bus contention.

CS[11]

AP[0]

Chip selectÑOutput that enable speciÞc memory devices or peripherals connected to MPC8260

buses.

Address parity 0Ñ(Input/output)The 60x master that drives the address bus, drives also the

address parity signals. The value driven on address parity 0 pin should give odd parity (odd number

of Ô1Õs) on the group of signals that includes address parity 0 and A[0Ð7].

Table 6-1. External Signals (Continued)

Signal Description

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......