MOTOROLA

Chapter 8. The 60x Bus

8-23

Part III. The Hardware Interface

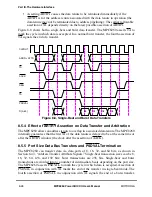

8.4.4 Address Transfer Termination

Address transfer termination occurs with the assertion of the address acknowledge (AACK)

signal, or retried with the assertion of ARTRY. ARTRY must remain asserted until one

clock after AACK; the bus clock cycle after AACK is called the ARTRY window. The

MPC8260 controls assertion of AACK unless the cycle is claimed by an external slave, such

as an external L2 cache controller. Following the assertion of L2_HIT, the L2 cache

controller is responsible for asserting AACK. When AACK is asserted by the external slave,

it should be asserted for one clock cycle and then negated for one clock cycle before

entering a high-impedance state. The MPC8260 holds AACK in a high-impedance state

until it is required to assert AACK to terminate the address cycle.

The MPC8260 uses AACK to enforce a pipeline depth of one to its internal slaves.

NOTE

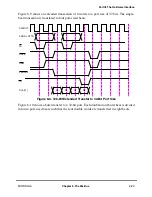

If the MPC8260 processor clock is conÞgured for 1x or 1.5x

clock mode, the ARTRY snoop response cannot be determined

in the minimum allowed address tenure period. For this clock

mode, AACK must not be asserted to the chip until at least the

third clock of the address tenure (one address wait state) to give

the processor time to assert ARTRY on the bus. For the other

clock conÞguration modes, the ARTRY snoop response can be

determined in the minimum address tenure period, and AACK

may be asserted as early as the second bus clock of the address

tenure (zero address wait states).

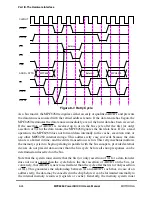

8.4.4.1 Address Retried

with ARTRY

The address transfer can be terminated with the requirement to retry if ARTRY is asserted

during the address tenure and through the cycle following AACK. The assertion causes the

entire transaction (address and data tenure) to be rerun. As a snooping device, the MPC8260

processor asserts ARTRY for a snooped transaction that hits modiÞed data in the data cache

that must be written back to memory, or if the snooped transaction could not be serviced.

As a bus master, the MPC8260 responds to an assertion of ARTRY by aborting the bus

transaction and requesting the bus again, as shown in Figure 8-7. Note that after

recognizing an assertion of ARTRY and aborting the current transaction, the MPC8260

may not run the same transaction the next time it is granted the bus.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......