19-10

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

The CP can be conÞgured to begin processing a new frame/buffer without waiting the

normal polling time by setting TODR[TOD] after TxBD[R] is set. Because this feature

favors the speciÞed TxBD, it may affect servicing of other SCC FIFOs. Therefore,

transmitting on demand should only be used when a high-priority TxBD has been prepared

and enough time has passed since the last g transmission. Table 19-3 describes TODR

Þelds.

19.2 SCC Buffer Descriptors (BDs)

Data associated with each SCC channel is stored in buffers and each buffer is referenced by

a buffer descriptor (BD) that can reside anywhere in dual-port RAM. The total number of

8-byte BDs is limited only by the size of the dual-port RAM (128 BDs/1 Kbyte). These BDs

are shared among all serial controllersÑSCCs, SMCs, SPI, and I

2

C. The user deÞnes how

the BDs are allocated among the controllers.

Each 64-bit BD has the following structure:

¥

The half word at 0x0 contains status and control bits that control and report

on the data transfer. These bits vary from protocol to protocol. The CPM updates the

status bits after the buffer is sent or received.

¥

The half word at 0x2 (data length) holds the number of bytes sent or

received.

Ñ For an RxBD, this is the number of bytes the controller writes into the buffer. The

CPM writes the length after received data is placed into the associated buffer and

the buffer closed. In frame-based protocols (but not including SCC transparent

operation), this Þeld contains the total frame length, including CRC bytes. Also,

if a received frameÕs length, including CRC, is an exact multiple of MRBLR, the

last BD holds no actual data but does contain the total frame length.

Ñ For a TxBD, this is the number of bytes the controller should send from its buffer.

Normally, this value should be greater than zero. The CPM never modiÞes this

Þeld.

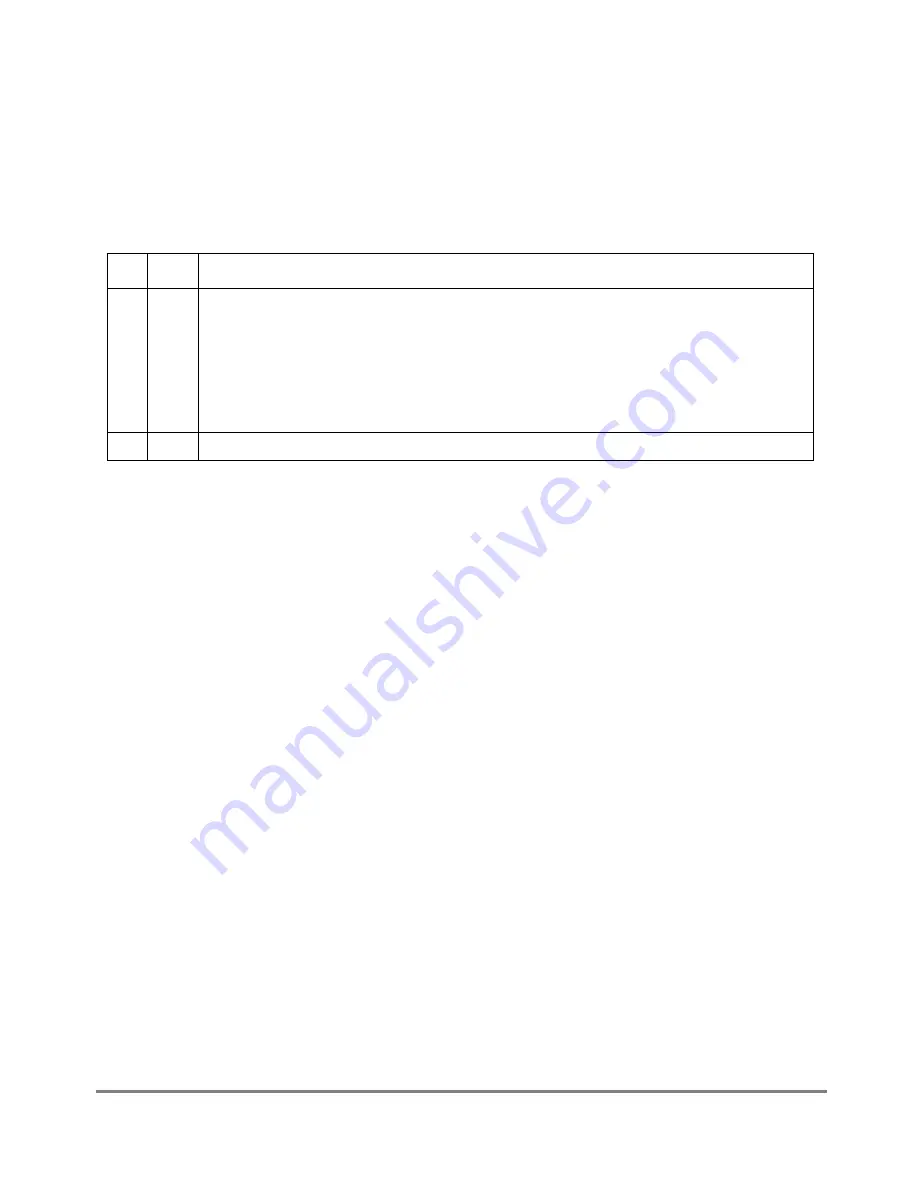

Table 19-3. TODR Field Descriptions

Bits

Name

Description

0

TOD

Transmit on demand.

0 Normal operation.

1 The CP gives high priority to the current TxBD and begins sending the frame without waiting the

normal polling time to check the TxBDÕs R bit. TOD is cleared automatically after one serial clock, but

transmitting on demand continues until an unprepared (R = 0) BD is reached. TOD does not need to

be set again if new TxBDs are added to the BD table as long as older TxBDs are still being

processed. New TxBDs are processed in order. The Þrst bit of the frame is typically clocked out 5-6

bit times after TOD is set.

1Ð15

Ñ

Reserved, should be cleared.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......