8-26

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

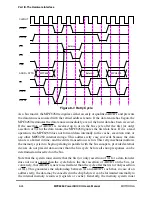

8.4.5 Pipeline Control

The MPC8260 supports the two following modes:

¥

One-level pipeline modeÑTo maintain the one-level pipeline, AACK is not asserted

for a pipelined address tenure until the current data tenure ends. In 60x-compatible

bus mode, a two-level pipeline depth can occur (for example, when an external 60x-

bus slave does not support one-level pipelining). When the internal arbiter counts a

pipeline depth of two (two assertions of AACK before the assertion of the current

data tenure) it negates all address bus grant (BG) signals.

¥

No-pipeline modeÑThe MPC8260 does not assert AACK until the corresponding

data tenure ends.

8.5 Data Tenure Operations

This section describes the operation of the MPC8260 during the data bus arbitration,

transfer, and termination phases of the data tenure.

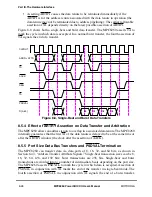

8.5.1 Data Bus Arbitration

The beginning of an address transfer, marked by the assertion of transfer start (TS), is also

an implicit data bus request provided that the transfer type signals (TT[0Ð4]) indicate that

the transaction is not address-only.

The MPC8260 arbiter supports one external master and uses DBG to grant the external

master data bus.The DBG signals are not asserted if the data bus, which is shared with

memory, is busy with a transaction.

A qualiÞed data bus grant (QDBG) can be expressed as the assertion of DBG while DBB

and ARTRY (associated with the data bus operation) are negated.

Note that the MPC8260 arbiter should assert DBG only when it is certain that the Þrst TA

will be asserted with or after the associated ARTRY. The MPC8260 DBG is asserted with

TS if the data bus is free and if the PPC_ACR[DBGD] = 0. If PPC_ACR[DBGD] = 1, DBG

is asserted one cycle after TS if the data bus is not busy. The DBG delay should be used to

ensure that ARTRY is not asserted after the Þrst or only TA assertion. For the programming

model, see Section 4.3.2.2, Ò60x Bus Arbiter ConÞguration Register (PPC_ACR).Ó

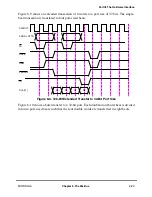

Note that DBB should not be asserted after the data tenure is Þnished. Assertion of DBB

after the last TA causes improper operation of the bus. (MPC8260 internal masters do not

assert DBB after the last TA.)

Note the following:

¥

External bus arbiters must comply with the following restriction on assertion of

DBG which is connected to the MPC8260. In case the data bus is not busy with the

data of a previous transaction on the bus, external arbiter must assert DBG in the

same cycle in which TS is asserted (by a master which was granted the bus) or in the

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......