MOTOROLA

Chapter 26. Serial Management Controllers (SMCs)

26-7

Part IV. Communications Processor Module

To extract data from a partially full receive buffer, issue a

CLOSE

RXBD

command.

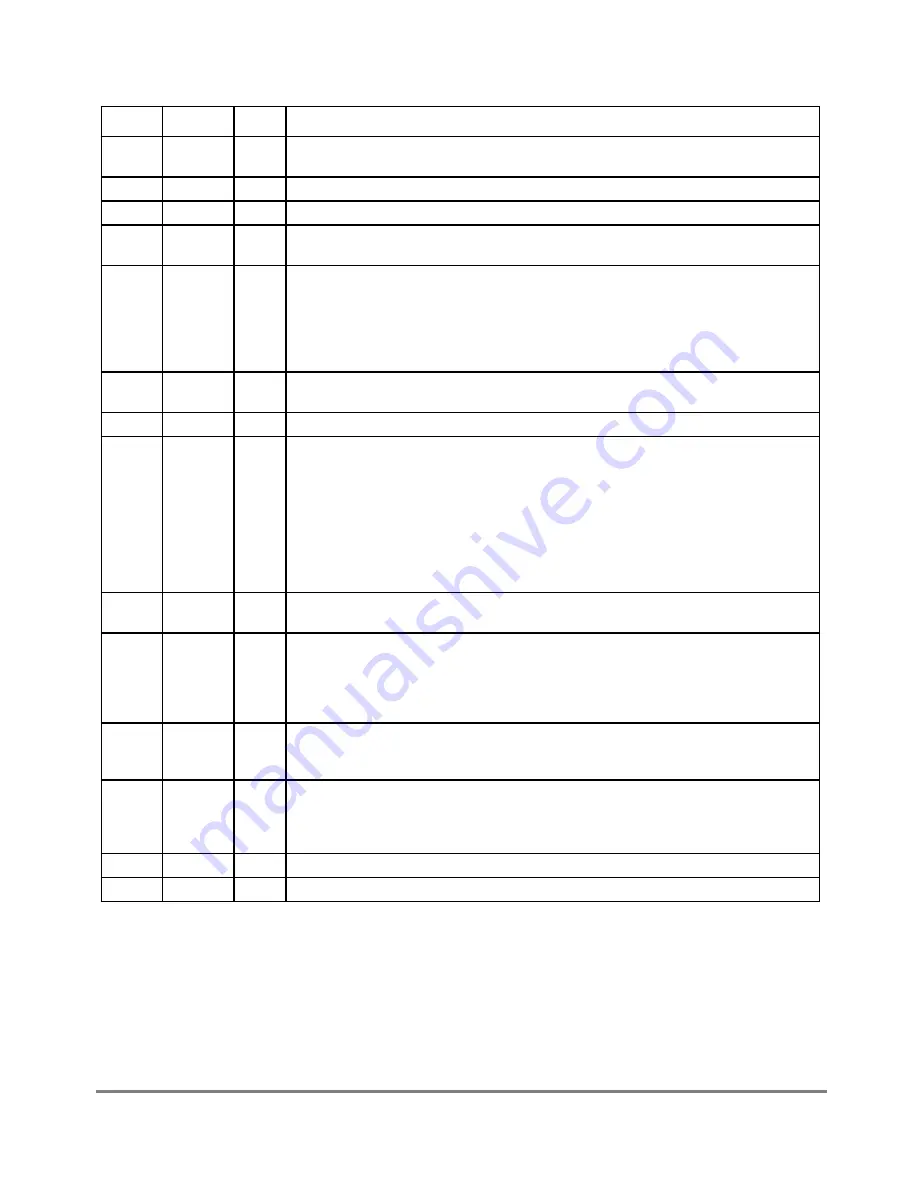

0x12

Ñ

Hword Rx internal byte count.

2

A down-count value initialized with the MRBLR value and

decremented with every byte the SDMA channels write.

0x14

Ñ

Word

Rx temp

2

Can be used only by the CP.

0x18

TSTATE

Word

Tx internal state.

2

Can be used only by the CP.

0x1C

Ñ

Word

Tx internal data pointer.

2

Updated by the SDMA channels to show the next address in

the buffer to be accessed.

0x20

TBPTR

Hword TxBD pointer. Points to the next BD for each SMC channel the transmitter transfers data

from when it is in idle state or to the current BD during frame transmission. After reset or

when the end of the table is reached, the CP initializes TBPTR to the TBASE value. Most

applications never need to write TBPTR, but it can be written when the transmitter is

disabled or when no transmit buffer is in use. For instance, after a

STOP

TRANSMIT

or

GRACEFUL

STOP

TRANSMIT

command is issued and the frame completes its transmission.

0x22

Ñ

Hword Tx internal byte count.

2

A down-count value initialized with the TxBD data length and

decremented with every byte the SDMA channels read.

0x24

Ñ

Word

Tx temp.

2

Can be used only by the CP.

0x28

MAX_IDL

Hword

Maximum idle characters. (UART protocol-speciÞc parameter) When a character is

received on the line, the SMC starts counting idle characters received. If MAX_IDL idle

characters arrive before the next character, an idle time-out occurs and the buffer closes,

which sends an interrupt request to the core to receive data from the buffer. MAX_IDL

demarcates frames in UART mode. Clearing MAX_IDL disables the function so the

buffer never closes, regardless of how many idle characters are received. An idle

character is calculated as follows: 1 + data length (5 to 14) + 1 (if parity bit is used) +

number of stop bits (1 or 2). For example, for 8 data bits, no parity, and 1 stop bit,

character length is 10 bits.

0x2A

IDLC

Hword

Temporary idle counter. (UART protocol-speciÞc parameter) Down-counter in which the

CP stores the current idle counter value in the MAX_IDL time-out process.

0x2C

BRKLN

Hword

Last received break length. (UART protocol-speciÞc parameter) Holds the length of the

last received break character sequence measured in character units. For example, if the

receive signal is low for 20 bit times and the deÞned character length is 10 bits, BRKLN =

0x002, indicating that the break sequence is at least 2 characters long. BRKLN is

accurate to within one character length.

0x2E

BRKEC

Hword

Receive break condition counter. (UART protocol-speciÞc parameter) Counts break

conditions on the line. A break condition may last for hundreds of bit times, yet BRKEC

increments only once during that period.

0x30

BRKCR

Hword

Break count register (transmit). (UART protocol-speciÞc parameter) Determines the

number of break characters the UART controller sends. Set when the SMC sends a

break character sequence after a

STOP

TRANSMIT

command. For 8 data bits, no parity, 1

stop bit, and 1 start bit, each break character is 10 zeros.

0x32

R_MASK

Hword

Temporary bit mask. (UART protocol-speciÞc parameter)

0x34

Ñ

Word

SDMA Temp

1

From the pointer value programmed in SMC

x

_BASE: SMC1_BASE at 0x87FC, SMC2_BASE at IMMR + 0x88FC.

2

Not accessed for normal operation. May hold helpful information for experienced users and for debugging.

Table 26-2. SMC UART and Transparent Parameter RAM Memory Map (Continued)

Offset

1

Name

Width

Description

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......