MOTOROLA

Chapter 30. Fast Ethernet Controller

30-19

Part IV. Communications Processor Module

30.17 Ethernet Error-Handling Procedure

The Ethernet controller reports frame reception and transmission error conditions using the

channel BDs, the error counters, and the FCC event register.

Transmission errors are described in Table 30-6.

Reception errors are described in Table 30-7.

30.18 Fast Ethernet Registers

The following sections describe registers used for conÞguring and operating the Fast

Ethernet controller.

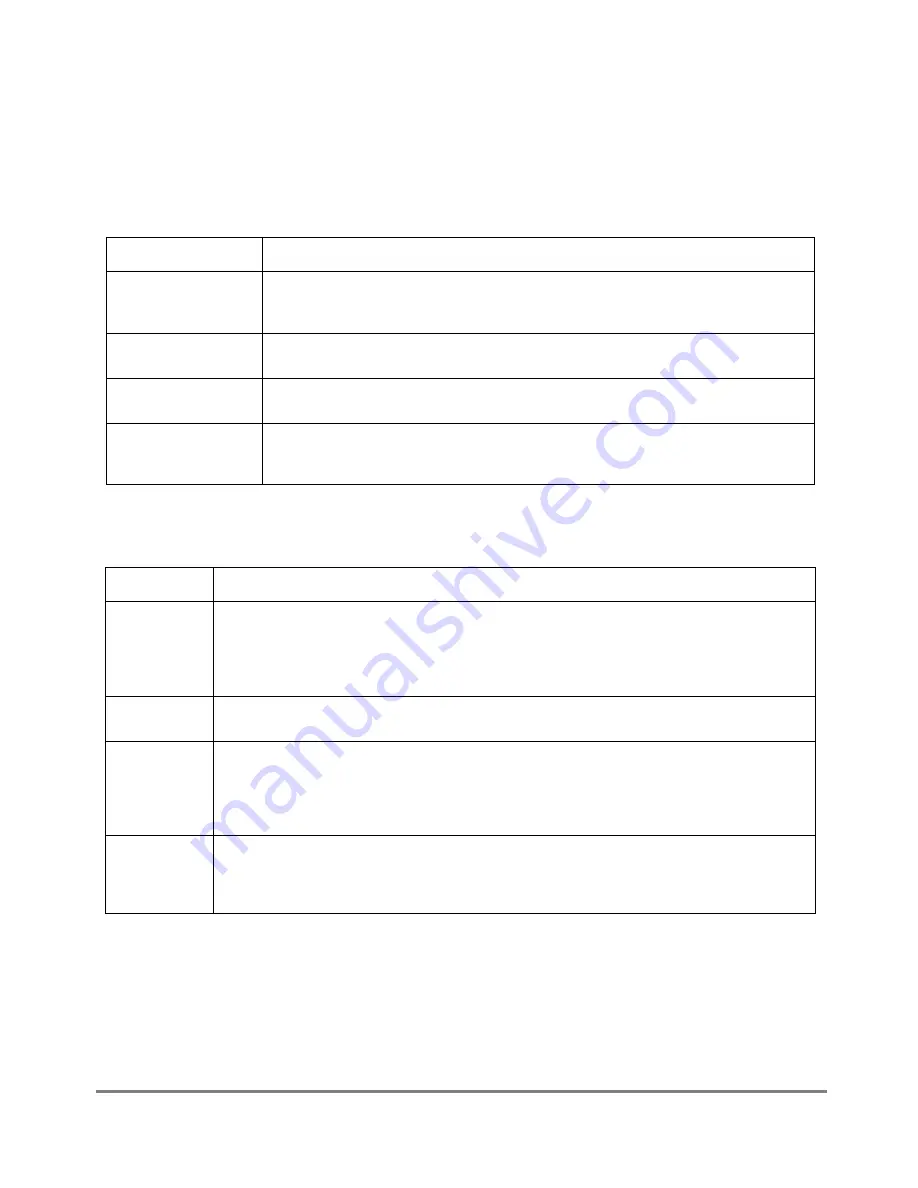

Table 30-6. Transmission Errors

Error

Response

Transmitter underrun

The controller sends 32 bits that ensure a CRC error, terminates buffer transmission, closes

the buffer, sets TxBD[UN] and FCCE[TXE]. The controller resumes transmission after

receiving the

RESTART

TRANSMIT

command.

Carrier sense lost during

frame transmission

If no collision is detected in the frame, the controller sets TxBD[CSL] and FCCE[TXE], and it

continues the buffer transmission normally. No retries are performed as a result of this error.

Retransmission

attempts limit expired

The controller terminates buffer transmission, closes the buffer, sets TxBD[RL] and

FCCE[TXE]. Transmission resumes after receiving the

RESTART

TRANSMIT

command.

Late collision

The controller terminates buffer transmission, closes the buffer, sets TxBD[LC] and

FCCE[TXE]. The controller resumes transmission after receiving the

RESTART

TRANSMIT

command. Note that late collision parameters are deÞned in FPSMR[LCW].

Table 30-7. Reception Errors

Error

Description

Overrun error

The Ethernet controller maintains an internal FIFO buffer for receiving data. If a receiver FIFO buffer

overrun occurs, the controller writes the received data byte to the internal FIFO buffer over the

previously received byte. The previous data byte and frame status are lost. The controller closes the

buffer, sets RxBD[OV] and FCCE[RXF], and increments the discarded frame counter (DISFC). The

receiver then enters hunt mode.

Busy error

A frame is received and discarded due to a lack of buffers. The controller sets FCCE[BSY] and

increments the discarded frame counter (DISFC).

Non-octet error

(dribbling bits)

The Ethernet controller handles a nibble of dribbling bits when the receive frame terminates as

nonoctet aligned and it checks the CRC of the frame on the last octet boundary. If there is a CRC

error, the frame nonoctet aligned (RxBD[NO]) error is reported, FCCE[RXF] is set, and the

alignment error counter (ALEC) in the parameter RAM is incremented. If there is no CRC error, no

error is reported.

CRC error

When a CRC error occurs, the controller closes the buffer, and sets RxBD[CR] and FCCE[RXF].

Also, the CRC error counter (CRCEC) in the parameter RAM is incremented. After receiving a frame

with a CRC error, the receiver enters hunt mode. CRC checking cannot be disabled, but the CRC

error can be ignored if checking is not required.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......