4-6

Memory Controller

4.5.3 Memory Timing Parameter Definitions

Programmable memory timing support is provided to allow for greater flexibility at the system level. As a

result, memory timing parameters may be adjusted to support faster SDRAM technologies as they become

available as well as to maximize the performance of the SDRAM memory subsystem. The timing parame-

ters listed in Table 24. are set via the SDTR1 register. See Section 4.9.2.1, “SDTR1 - SDRAM Timing Reg-

ister 1” for more information.

64-bit

(72-bit ECC)

contiguous column address bits = 9

2

9

=512 unique column addresses

data width 64-bit = 8 byte

page size = 512 x 8byte = 4KByte

contiguous column address bits = 8

2

8

=256 unique column addresses

data width 64-bit = 8 byte

page size = 256 x 8byte = 2KByte

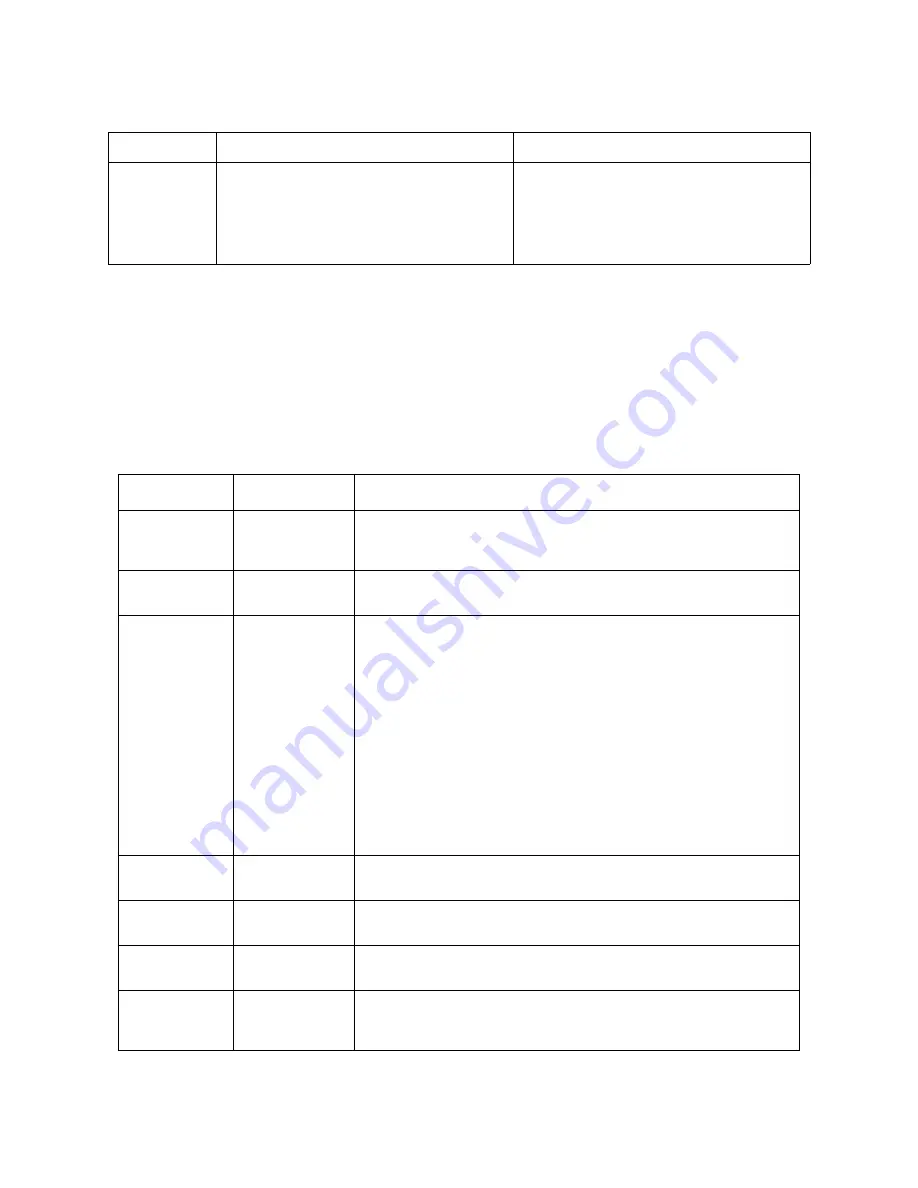

Table 24. SDRAM Memory Timing Parameters

Name

Function

Description

SD_RCD

Activate to

Read/Write

Command

Minimum number of clock cycles from an Activate Command to a

Read or Write Command. Corresponds to DRAM RAS_ to CAS_

assertion delay.

SD_RFTA

Refresh to Acti-

vate

Minimum number of clock cycles from a CBR Refresh Command

to the next Activate Command.

SD_RTP

Read to Pre-

charge

Non Auto-Precharge Mode.

The value programmed in this field should be determined empiri-

cally based upon the expected pattern of memory acceses. If

consecutive accesses typically are within the same page, a larger

value will provide improved memory subsystem performance. If

consecutive accesses are typically to different pages, a smaller

value is recommended. The programmed value sets the number

of clock cycles from a Read Command to the SDRAM Controller

issuing a Precharge Command.

Auto Precharge Mode.

Page Hits are not possible if the SDRAM uses Auto Precharge

mode. When using this mode, this register location should be pro-

grammed with the number of clock cycles from a Read with Auto-

Precharge Command to the beginning of Auto-Precharge.

SD_WTP

Write to Pre-

charge

Same description as SD_RTP field

SD_PTA

Precharge to

Active

Minimum number of clock cycles required to wait following a Pre-

charge Command to issuing the next Activate Command.

SD_SREX

Self-Refresh

Exit delay

Number of clock cycles until first access allowed following self-re-

fresh exit.

SD_RRD

Bank A Acti-

vate to Bank B

Activate

Module Bank-to-Bank Activate Delay.

Hardcoded to 2 clock cycles. Pertains to sub-banks only.

Table 23. Determining Maximum Page Size (Continued)

mode 1-3

mode 4

Summary of Contents for CPC700

Page 10: ...Table of Contents x Table of Contents...

Page 16: ...Tables xvi List of Tables...

Page 28: ...1 12 CPC700 User s Manual Preliminary...

Page 72: ...3 36 Processor Interface...

Page 132: ...4 60 Memory Controller...

Page 184: ...5 52 PCI Interface...

Page 194: ...6 10 Clock Power Management and Reset...

Page 224: ...8 18 IIC...

Page 244: ...10 10 Interrupt Controller...

Page 246: ...I 11 2 JTAG...

Page 250: ...12 4 Processor Local Bus PLB...

Page 262: ...14 10 Register Summary...

Page 267: ...CPC700 User s Manual Preliminary...