FSB Design Guidelines

R

44

Intel

®

855PM Chipset Platform Design Guide

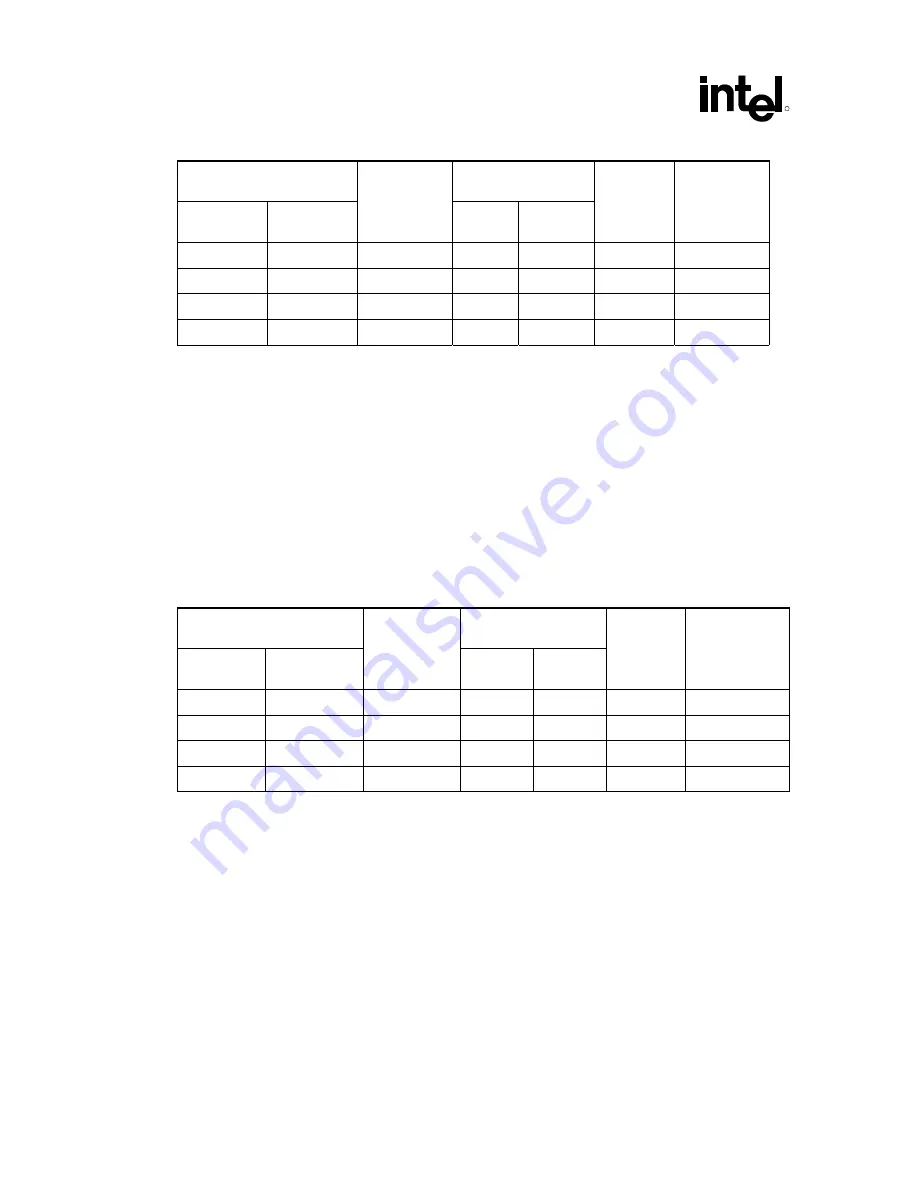

Table 4. FSB Source Synchronous Data Signal Routing Guidelines Topology 1

Signal Names

Total Trace Length

CPU MCH

Transmission

Line Type

Min

(inches)

Max

(inches)

Nominal

Impedance

(

)

Width &

spacing (mils)

DINV[3:0]#

DBI[3:0]#

Strip-line

0.5

5.5

55 ± 15%

4 & 12

D[63:0]#

HD[63:0]#

Strip-line

0.5

5.5

55 ±15%

4 & 12

DSTBN[3:0]# HDSTBN[3:0]#

Strip-line

0.5

5.5

55 ± 15%

4 & 12

DSTBP[3:0]# HDSTBP[3:0]#

Strip-line

0.5

5.5

55 ±15%

4 & 12

If routing space constraints do not allow 1:3 spacing of the source synchronous data signals, Table 5

lists alternative routing requirements for some of these signals if 1:2 spacing is used. In both topologies,

the pin-to-pin trace length should be limited to a minimum of 0.5 inches and a maximum of 5.5 inches.

The adherence to tighter characteristic trace impedance tolerances for the alternative routing

requirements allows the closer spacing of the data and bus inversion signals to be achieved. The use of ±

10% tolerance for the trace impedance in the alternative topology allows designs to maintain the same

overall minimum and maximum trace lengths as the primary topology that utilizes a looser ± 15%

tolerance. Although the data and bus inversion signals for the FSB can be routed with 1:2 spacing when

using the tighter trace impedance tolerance, the data strobes

must

maintain 1:3 spacing. In this case, the

processor’s DSTBN[3:0]# and DSTBP[3:0]# strobe signals must be routed to the MCH’s

HDSTBN[3:0]# and HDSTBP[3:0]# strobe signals with 1:3 spacing from all signals even if ± 10% trace

impedance tolerance is used.

Table 5. FSB Source Synchronous Data Signal Routing Guidelines Topology 2

Signal Names

Total Trace Length

CPU MCH

Transmission

Line Type

Min

(inches)

Max

(inches)

Nominal

Impedance

(

)

Width & spacing

(mils)

DINV[3:0]#

DBI[3:0]#

Strip-line

0.5

5.5

55 ± 10%

4 & 8

D[63:0]#

HD[63:0]#

Strip-line

0.5

5.5

55 ± 10%

4 & 8

DSTBN[3:0]#

HDSTBN[3:0]#

Strip-line

0.5

5.5

55 ±10%

4 & 12

DSTBP[3:0]#

HDSTBP[3:0]#

Strip-line

0.5

5.5

55 ± 10%

4 & 12

4.1.3.3.

Source Synchronous – Address

Source synchronous address signals operate at 200 MHz. Thus, their routing requirements are very

similar to the data signals. Refer to Sections 4.1.3.1 and 4.1.3.2 for further details. Table 6 details the

partition of the address signals into matched length groups. Due to the lower operating frequency of the

address signals, pin-to-pin length matching is relaxed to ± 200 mils. Each group is associated with only

one strobe signal. To maximize setup/hold time margin, the address strobes should be trace length

matched to the average trace length of the address signals of their associated group. In addition, each

address signal should be trace length matched within ± 200 mils of its associated strobe signal.