Platform Design Checklist

R

276

Intel

®

855PM Chipset Platform Design Guide

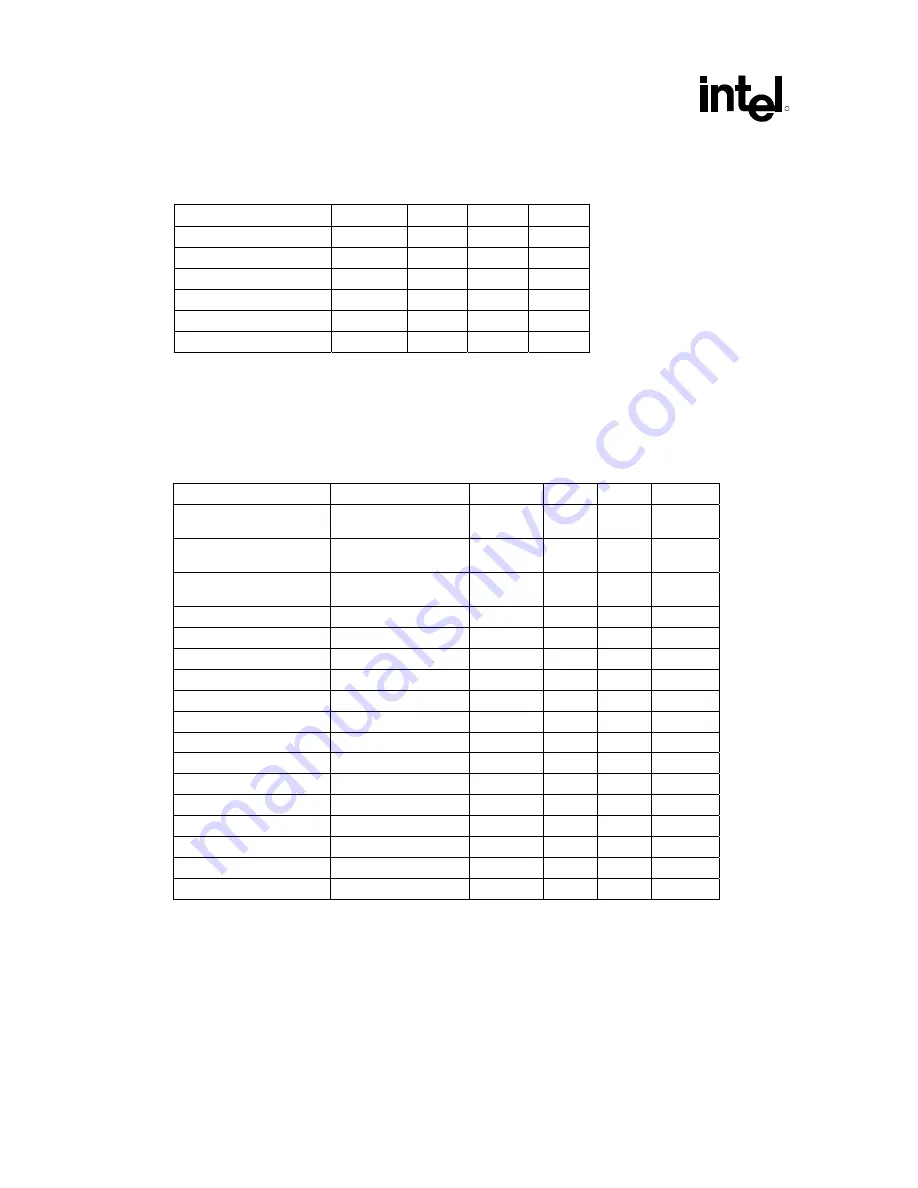

14.2. Customer

Implementation

Fill in Schematic Name of Voltage Rails on Mark Boxes of when Rails are powered on.

Name of Rail

On S0-S1

On S3

On S4

On S5

14.3.

Design Checklist Implementation

The voltage rail designations in this design checklist were intended to be as general as possible. The

following table describes the equivalent voltage rails in the Intel CRB schematics attached in this design

guide.

Checklist Rail

Intel CRB Rail

On S0-S1

On S3

On S4

On S5

Vcc1_2[Vcc_mch] V1.2S_MCH X

Vcc1_25[DDR_Vtt]

4

V1.25S X

Vcc1_5 V1.5S,

1.5S_AGP

X

VccSus1_5 V1.5,

V1.5ALWAYS

X

X

1,3

1,3

V1_5ALWAYS See

VccSus1_5

X

X

X

X

Vcc1_8 V1-8S

X

VccSus2_5 V2.5_MCH,

V2.5DDR

X X

Vcc3_3 V3S,

V3.3S_ICH

X

VccSus3_3

V3, V3ALWAYS

X

X

1, 3

1, 3

VccSus3_3LAN V3.3_LAN X

2

2

2

V3ALWAYS See

VccSus3_3

X

X

X

X

Vcc5 V5S

X

VccSus5 V5

X

X

1

1

Vcc12 V12S

X

VccRTC VccRTC

X

X

X

X

VCCP

5

VCCP X

VCC[Vcc_Core] Vcc_core X

NOTES:

1.

A rail powered in Sx is dependent on implementation.

2.

A VccLANx rail powered on in Sx is dependent on implementation.

3.

A VxALWAYS rail can be the SUS rail depending on implementation.

4.

Vcc1_25 is the 1.25V VTT termination voltage for DDR. This power rail can be OFF during S3.

5.

VCCP is the 1.05V FSB signaling level of the CPU, MCH, and ICH4-M (legacy signal). Also used for the ITP700

FLEX debug port, if used.