595

CHAPTER 19 512 KBIT FLASH MEMORY

19.7.3

Timing Limit Over Flag (DQ5)

The timing limit over flag (DQ5) is a hardware sequence flag that notifies flash memory

that the execution of the automatic algorithm has exceeded a prescribed time (the time

required for programming/erasing).

■

Timing Limit Over Flag (DQ5)

"State Transition of Timing Limit Over Flag (State Change at Normal Operation)" and

"State Transition of Timing Limit Over Flag (State Change at Abnormal Operation"

give the state transition of the timing limit over flag.

●

At programming and chip/sector erasing

•

If a read access is made after starting the automatic algorithm for programming or chip /sector

erasing and it is within a prescribed time (the time required for programming/erasing), the

timing limit over flag (DQ5) outputs 0. If it exceeds the prescribed time, the timing limit over

flag (DQ5) outputs 1.

•

The timing limit over flag (DQ5) can be used to identify the success or failure of programming/

erasing, regardless of whether the automatic algorithm is in progress or terminated. If the

automatic algorithm by the data polling or the toggle bit function is in execution when the

timing limit over flag (DQ5) outputs 1, programming can be identified as a failure.

•

For example, when 1 is set to the flash memory address with 1 set the flash memory,

programming fails. In this case, the flash memory will be locked and the automatic algorithm

will not complete. Therefore, no valid data is output from the data polling flag (DQ7). Also, the

toggle bit flag (DQ6) does not stop the toggle operation and exceeds the time limit, causing the

timing limit over flag (DQ5) to output 1. This state means that the flash memory is not being

used correctly; it does not mean that the flash memory is faulty. When this state occurs,

execute the reset command.

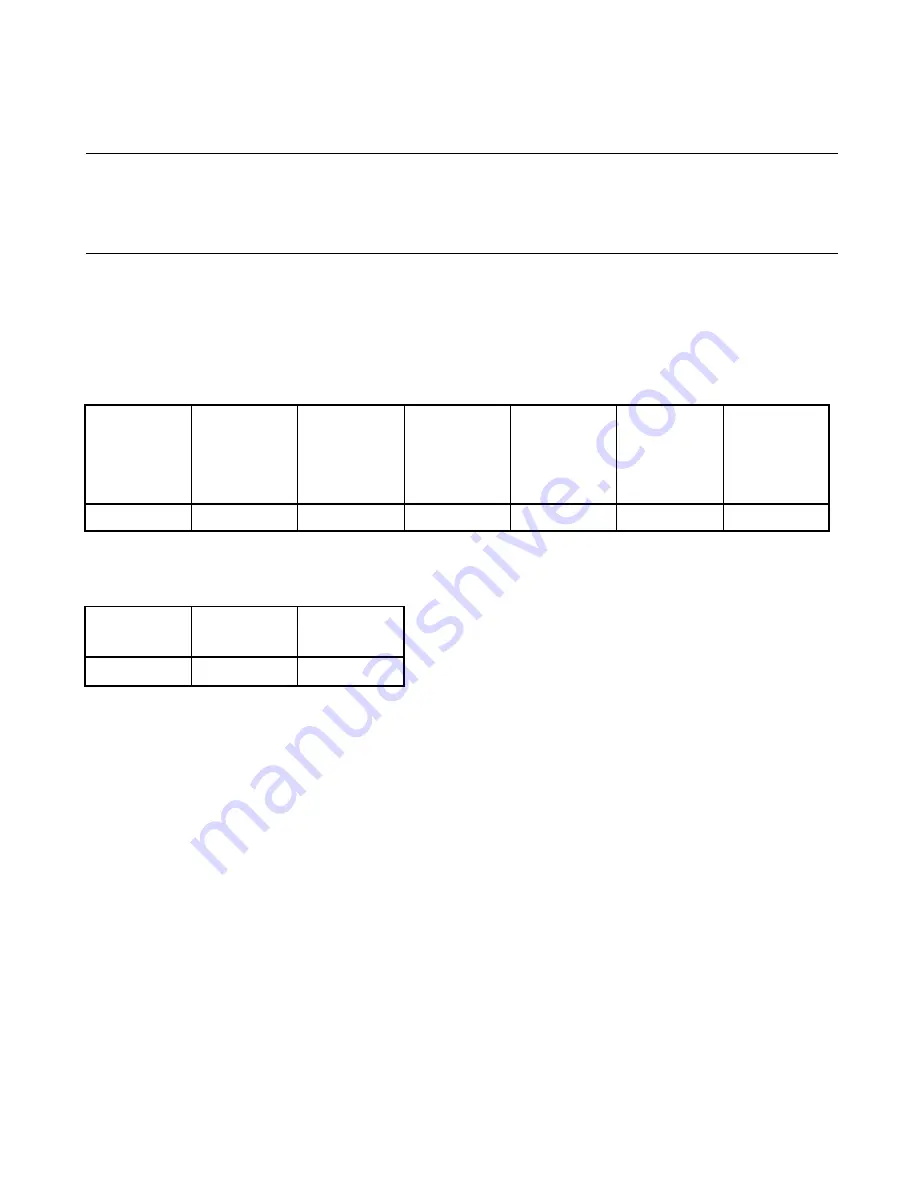

Table 19.7-7 State Transition of Timing Limit Over Flag (State Change at Normal Operation)

Operating State

Programming

→

Completed

Chip and

Sector Erasing

→

Completed

Wait for Sector

Erasing

→

Started

Sector Erasing

→

Erasing

Suspended

(Sector being

Erased)

Sector Erasing

Suspended

→

Resume

(Sector being

Erased)

Sector Erasing

being

Suspended

(Sector not

being Erased)

DQ5

0

→

DATA

:5

0

→

1

0

0

0

DATA

:5

Table 19.7-8 State Transition of Timing Limit Over Flag (State Change at Abnormal Operation

Operating

State

Programming

Chip and

Sector Erasing

DQ5

1 1

Summary of Contents for F2MC-16LX Series

Page 2: ......

Page 3: ...FUJITSU LIMITED F2MC 16LX 16 bit Microcontroller MB90895 series Hardware Manual ...

Page 4: ......

Page 8: ...iv ...

Page 10: ...vi ...

Page 36: ...18 CHAPTER 2 HANDLING DEVICES ...

Page 176: ...158 CHAPTER 3 CPU ...

Page 224: ...206 CHAPTER 5 Timebase timer ...

Page 294: ...276 CHAPTER 8 16 bit reload timer ...

Page 366: ...348 CHAPTER 12 DTP external interrupt ...

Page 398: ...380 CHAPTER 13 8 10 bit A D converter ...

Page 446: ...428 CHAPTER 14 UART0 ...

Page 588: ...570 CHAPTER 17 Address Match Detecting Function ...

Page 626: ...608 CHAPTER 19 512 KBIT FLASH MEMORY ...

Page 676: ...658 APPENDIX Table A 9 3 Bit Operation Instruction Map first byte 6CH ...

Page 678: ...660 APPENDIX Table A 9 5 2 byte Instruction Map first byte 6FH MUL MULW DIVU A A A ...

Page 680: ...662 APPENDIX Table A 9 7 ea Instruction 2 first byte 71H ...

Page 681: ...663 APPENDIX A Instructions Table A 9 8 ea Instruction 3 first byte 72H ...

Page 682: ...664 APPENDIX Table A 9 9 ea Instruction 4 first byte 73H ...

Page 683: ...665 APPENDIX A Instructions Table A 9 10 ea Instruction 5 first byte 74H ...

Page 684: ...666 APPENDIX Table A 9 11 ea Instruction 6 first byte 75H ...

Page 685: ...667 APPENDIX A Instructions Table A 9 12 ea Instruction 7 first byte 76H ...

Page 686: ...668 APPENDIX Table A 9 13 ea Instruction 8 first byte 77H ...

Page 687: ...669 APPENDIX A Instructions Table A 9 14 ea Instruction 9 first byte 78H ...

Page 688: ...670 APPENDIX Table A 9 15 MOVEA RWi ea Instruction first byte 79H ...

Page 689: ...671 APPENDIX A Instructions Table A 9 16 MOV Ri ea Instruction first byte 7AH ...

Page 690: ...672 APPENDIX Table A 9 17 MOVW RWi ea Instruction first byte 7BH ...

Page 691: ...673 APPENDIX A Instructions Table A 9 18 MOV ea Ri Instruction first byte 7CH ...

Page 692: ...674 APPENDIX Table A 9 19 MOVW ea Rwi Instruction first byte 7DH ...

Page 693: ...675 APPENDIX A Instructions Table A 9 20 XCH Ri ea Instruction first byte 7EH ...

Page 694: ...676 APPENDIX Table A 9 21 XCHW RWi ea Instruction first byte 7FH ...

Page 710: ......