g. With signal common mode as (V

REF+

+ GNDA).

h. This parameter is defined as the average of the differential inputs.

i. As shown in Figure 27-29 on page 1866, R

ADC

is the total equivalent resistance in the input line all the way up to the sampling

node at the input of the ADC.

j. See “System Clock Specification with ADC Operation” on page 1842 for full ADC clock frequency specification.

k. ADC conversion time (Tc) includes the ADC sample time (Ts).

l. Low noise environment is assumed in order to obtain values close to spec. Board must have good ground isolation between

analog and digital grounds, a clean reference voltage is assumed, and input signal must be bandlimited to Nyquist

bandwidth. No anti-aliasing filter is provided internally.

m. ADC static measurements taken by averaging over several samples. At least 20-sample averaging is assumed to obtain

expected typical or maximum spec values.

n. 12-bit DNL

o. Gain error is measured at max code after compensating for offset. Gain error is equivalent to "Full Scale Error." It can be

given in % of slope error, or in LSB, as done here.

p. Total Unadjusted Error is the maximum error at any one code versus the ideal ADC curve. It includes all other errors

(offset error, gain error and INL) at any given ADC code.

q. A low noise environment is assumed in order to obtain values close to spec. The board must have good ground isolation

between analog and digital grounds and a clean reference voltage. The input signal must be band-limited to Nyquist

bandwidth. No anti-aliasing filter is provided internally.

r. ADC dynamic characteristics are measured using low-noise board design, with low-noise reference voltage ( < -74dB

noise level in signal BW) and low-noise analog supply voltage. Board noise and ground bouncing couple into the ADC

and affect dynamic characteristics. Clean external reference must be used to achieve shown specs.

s. Differential signal with correct common mode, applied between two ADC inputs.

t. SDR = -THD in dB.

u. For higher frequency inputs, degradation in SDR should be expected.

v. SNDR = S/(N+D) = SINAD (in dB)

w. Effective number of bits (ENOB) can be calculated from SNDR: ENOB = (SNDR - 1.76) / 6.02.

x. Single ended inputs are more sensitive to board and trace noise than differential inputs; SNR and SNDR measurements

on single-ended inputs are highly dependent on how clean the test set-up is. If the input signal is not well-isolated on

the board, higher noise than specified could potentially be seen at the ADC output.

y. Note that this parameter does not include ADC error.

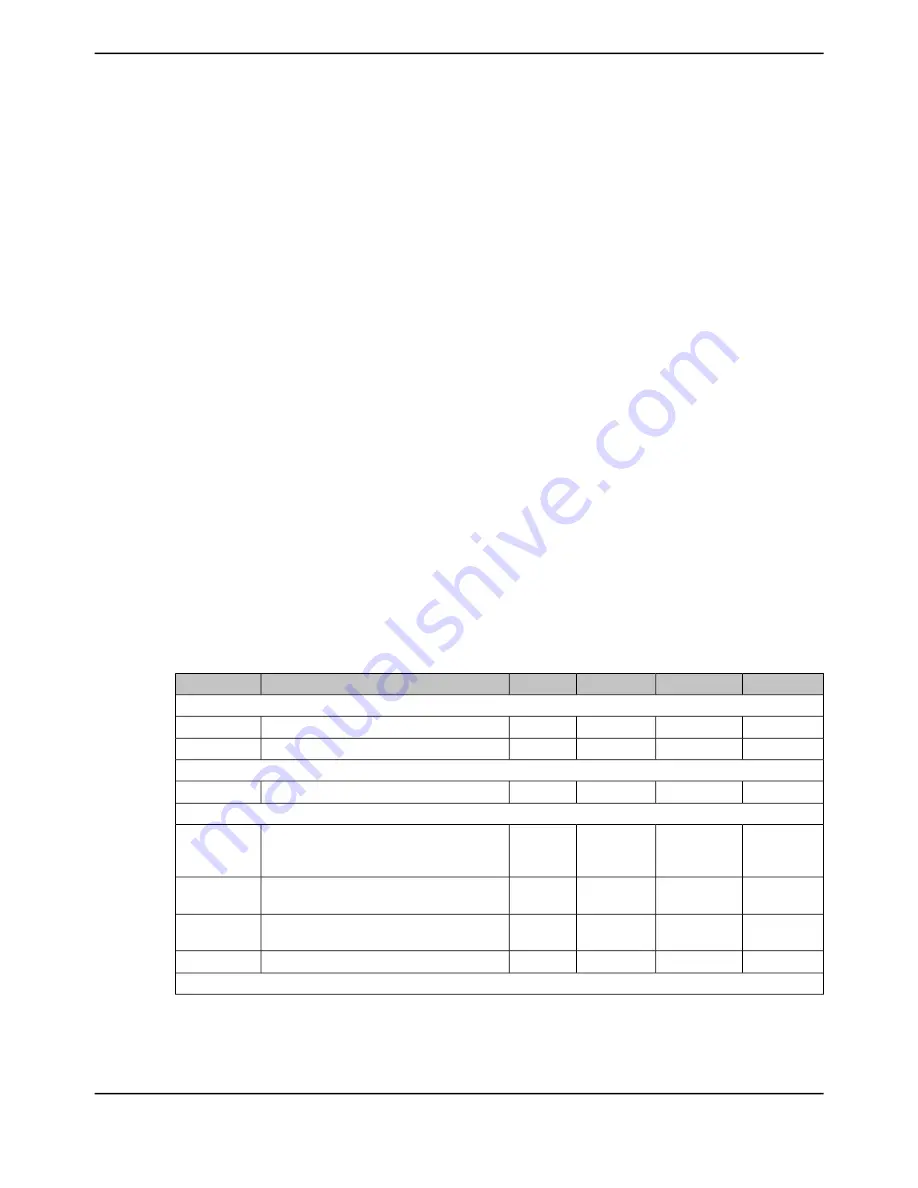

Table 27-45. ADC Electrical Characteristics for ADC at 2 Msps

ab

Unit

Max

Nom

Min

Parameter Name

Parameter

POWER SUPPLY REQUIREMENTS

V

3.63

3.3

2.97

ADC supply voltage

V

DDA

V

-

0

-

ADC ground voltage

GNDA

VDDA / GNDA VOLTAGE REFERENCE

μF

-

1.0 // 0.01

c

-

Voltage reference decoupling capacitance

C

REF

EXTERNAL VOLTAGE REFERENCE INPUT

V

V

DDA

V

DDA

2.4

Positive external voltage reference for ADC,

when

VREF

field in the

ADCCTL

register is

0x1

d

-

V

REFA+

µA

440

330.5

-

Current on

VREF+

input, using external V

REF+

= 3.3 V

I

VREF

µA

2.0

-

-

DC leakage current on

VREF+

input when

external VREF disabled

I

LVREF

μF

-

1.0 // 0.01

c

-

External reference decoupling capacitance

d

C

REF

ANALOG INPUT

1863

June 18, 2014

Texas Instruments-Production Data

Tiva

™

TM4C1294NCPDT Microcontroller