Inter-Integrated Circuit Controller

7-90

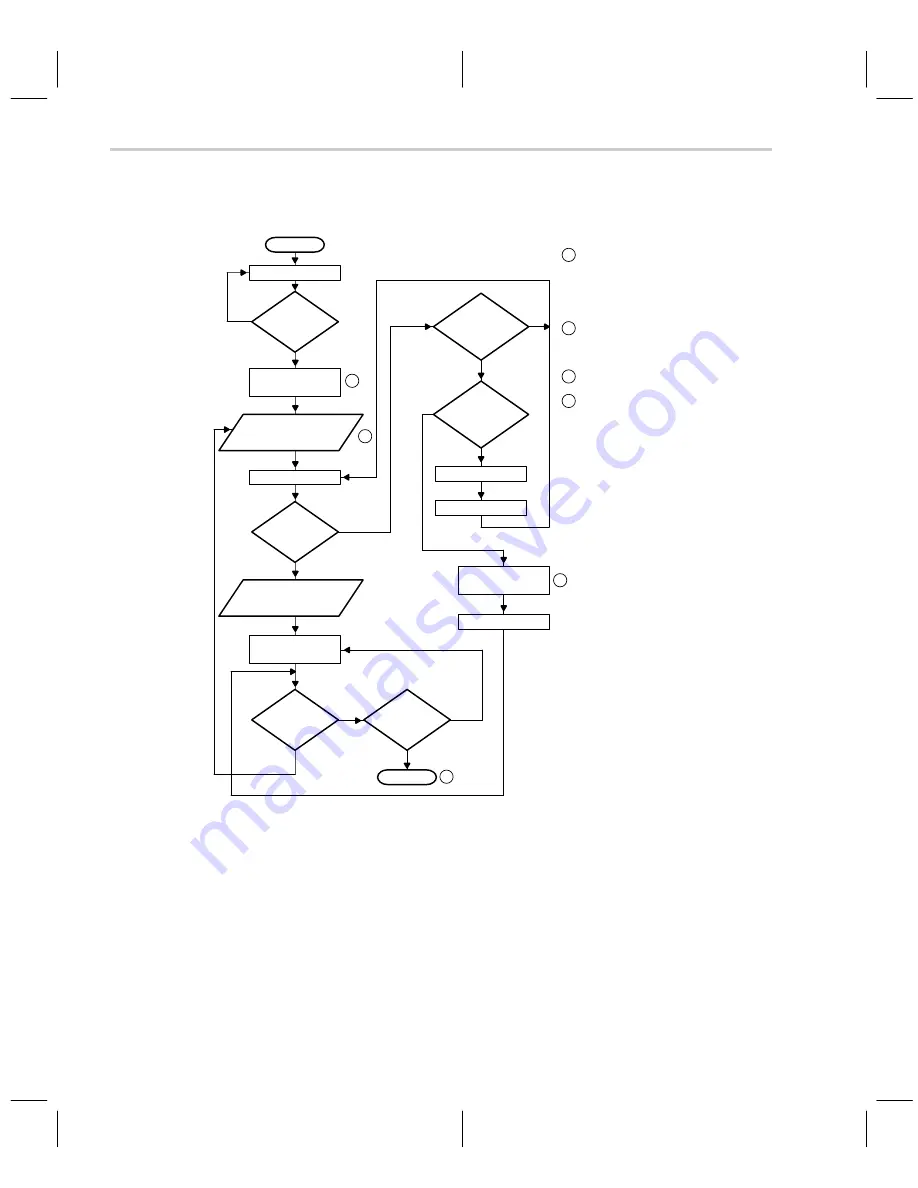

Figure 7–33. Master Receiver Mode, RM = 1, Polling 1 (Software Counter, Number of the

Receive Data Fixed)

Start

Is

bus free

(BB=0)

?

Write I2C_CON

with 8405h.

End

Read I2C_STAT.

No

Yes

1

n = 0 (data byte counter):

m = Number of data bytes

to be transferred

Read I2C_STAT.

Is

ACK returned

(NACK=0)

?

2

STT and STP are

cleared to 0 by hardware.

No

Yes

Reprogram

the registers.

STT = 1

(new start)

?

Yes

No

STP = 1

?

No

3

Read I2C_DATA.

n = n + 2

Are

m bytes

transferred

(n. = m)

?

Is

send data

being requested

(XUDF=1)

?

Yes

No

Yes

No

Set appropriate values to every

bit of I2C_CON. I2C_EN bit must be set

to 1 to take I2C out of reset condition. Setting

I2C_EN and setting other mode bits can be done

simultaneously.

Because RM=1. hardware counter does not run.

Thus, software counter counts the number of the

required transfer.

The I2C goes into slave receiver mode.

Set STP = 1

[EXPECTED COMMAND]

At the beginning,

(STT,STP) = (1.0)

in the middle,

(STT, STP) = (0.0)

At the end,

(STT, STP) = (0.1)

[EXPECTED I2C_IE]

I2C_IE = 00000b

3

2

1

Reprogram

the registers.

Read I2C_DATA.

Yes

4

4