Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

August 2006

Developer’s Manual

Order Number: 306262-004US

885

I2C Bus Interface Unit—Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

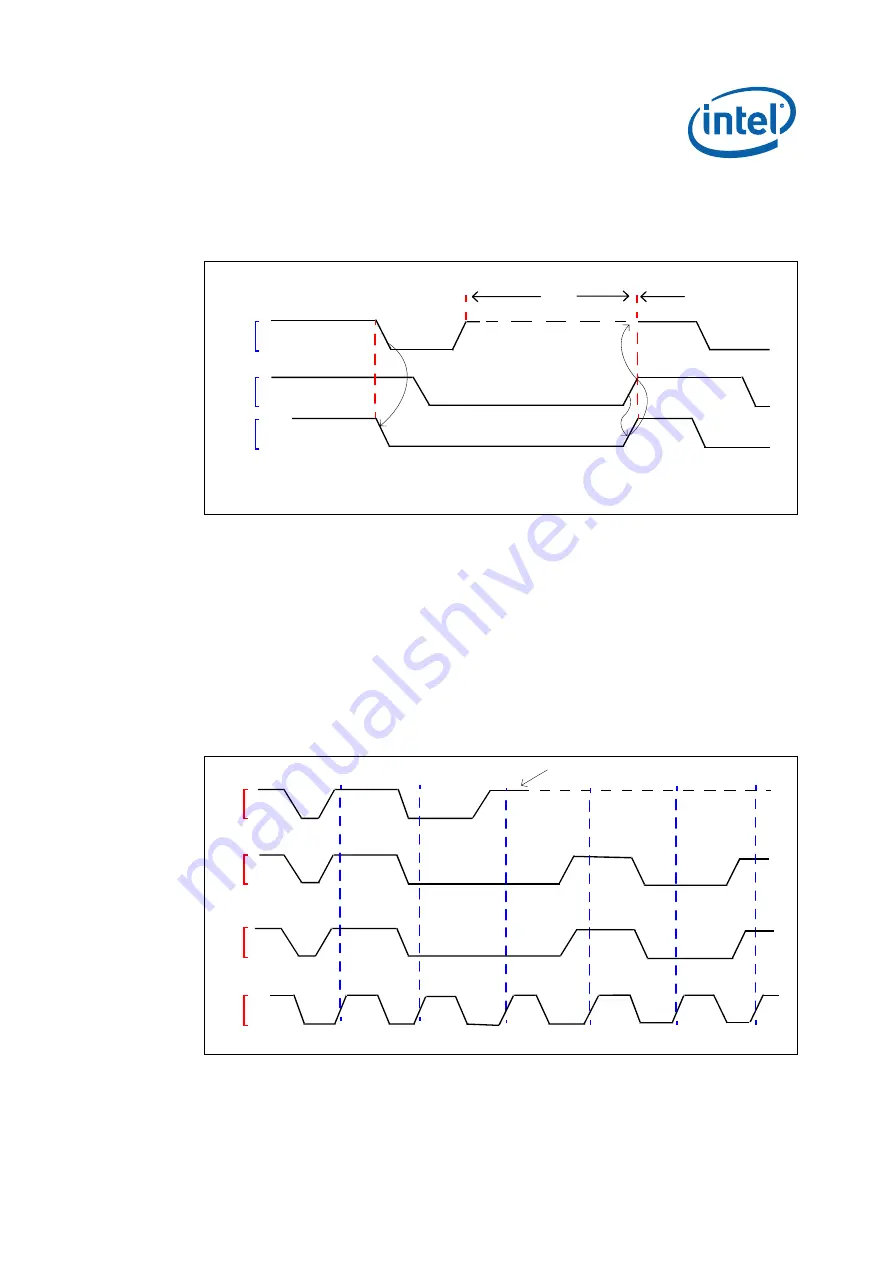

SCL line. Masters with shorter periods are held in a high wait-state during this time.

Once the master with the longest period completes, the SCL line transitions to the high

state, masters with the shorter periods can continue the data cycle.

21.5.4.2

SDA Arbitration

Arbitration on the SDA line can continue for a long period starting with the address and

R/W# bits and continuing with the data bits.

shows the arbitration

procedure for two masters (more than two may be involved depending on how many

masters are connected to the bus). When the address bit and the R/W# are the same,

the arbitration is then handled by the logic level of the data that is being driven. Due to

the wired-AND nature of the I

2

C bus, no data is lost when both (or all) masters are

outputting the same bus states. When the address, R/W# bit, or data is different, the

master that output the first high data bit loses arbitration and shuts its data drivers off.

When the I

2

C unit loses arbitration, it shuts off the SDA or SCL drivers for the

remainder of the byte transfer, sets the arbitration loss detected ISR bit, then returns

to idle (Slave-Receive) mode.

Figure 196. Clock Synchronization During the Arbitration Procedure

B4261-01

CLK2

SCL

Wait

State

Start Counting

High Period

CLK1

The first master to complete its high

period pulls the

SCL

line low.

The master with the longest clock

period holds the

SCL

line low.

Figure 197. Arbitration Procedure of Two Masters

B4262-01

SDA

SCL

Data 1

Data 2

Transmitter 1 Leaves Arbitration

Data 1 SDA