Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors—USB 2.0 Host Controller

Intel

®

IXP45X and Intel

®

IXP46X Product Line of Network Processors

Developer’s Manual

August 2006

410

Order Number: 306262-004US

9.14.1

Host Controller Initialization

After initial power-on or HCReset (hardware or via HCReset bit in the USBCMD

register), all of the operational registers will be at their default values, as illustrated in

Table 167, “Default Values of Operational Register Space” on page 410

. After a

hardware reset, only the operational registers not contained in the Auxiliary power well

will be at their default values.

In order to initialize the host controller, software should perform the following steps:

• Program the CTRLDSSEGMENT register with 4-Gigabyte segment where all of the

interface data structures are allocated.

• Write the appropriate value to the USBINTR register to enable the appropriate

interrupts.

• Write the base address of the Periodic Frame List to the PERIODICLIST BASE

register. If there are no work items in the periodic schedule, all elements of the

Periodic Frame List should have their T-Bits set to a one.

• Write the USBCMD register to set the desired interrupt threshold, frame list size (if

applicable) and turn the host controller ON via setting the Run/Stop bit.

• Write a 1 to CONFIGFLAG register to route all ports to the EHCI controller (see

Section 9.14.2, “Port Routing and Control” on page 411

).

At this point, the host controller is up and running and the port registers will begin

reporting device connects, etc. System software can enumerate a port through the

reset process (where the port is in the enabled state). At this point, the port is active

with SOFs occurring down the enabled port enabled High-speed ports, but the

schedules have not yet been enabled. The EHCI Host controller will not transmit SOFs

to enabled Full- or Low-speed ports. In order to communicate with devices via the

asynchronous schedule, system software must write the ASYNDLISTADDR register with

the address of a control or bulk queue head. Software must then enable the

asynchronous schedule by writing a one to the Asynchronous Schedule Enable bit in the

USBCMD register. In order to communicate with devices via the periodic schedule,

system software must enable the periodic schedule by writing a one to the Periodic

Schedule Enable bit in the USBCMD register. Note that the schedules can be turned on

before the first port is reset (and enabled).

Any time the USBCMD register is written, system software must ensure the appropriate

bits are preserved, depending on the intended operation.

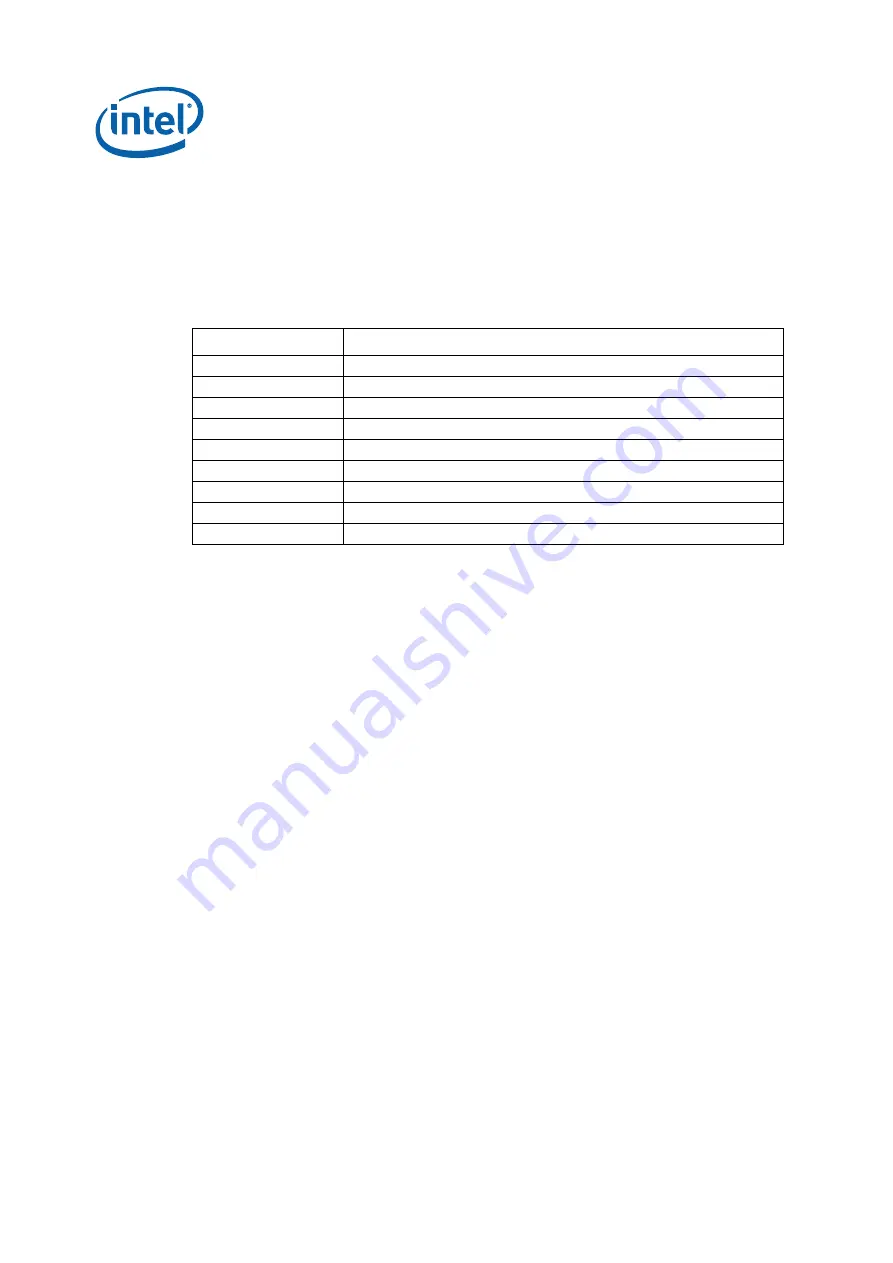

Table 167.

Default Values of Operational Register Space

Operational Register

Default Value (after Reset)

USBCMD

0x00080000 (0x00080B00 if Asynchronous Schedule Park Capability is a one)

USBSTS 0x00001000

USBINTR 0x00000000

FRINDEX 0x00000000

CTRLDSSEGMENT 0x00000000

PERIODICLISTBASE Undefined

ASYNCLISTADDR Undefined

CONFIGFLAG 0x00000000

PORTSC 0x00002000

(w/PPC set to one); 0x00003000 (w/PPC set to a zero)