MOTOROLA

Chapter 30. Serial Management Controllers

30-11

Part V. The Communications Processor Module

30.3.3 SMC UART Channel Transmission Process

The UART transmitter is designed to work with almost no intervention from the core. When

the core enables the SMC transmitter, it starts sending idles, which are deÞned as the full

character length of logic high. The SMC immediately polls the Þrst BD in the transmit

channel BD table and once every character time after that, depending on character length.

When there is a message to transmit, the SMC fetches data from memory and starts sending

the message.

When a BD data is completely written to the transmit FIFO, the SMC writes the message

status bits into the BD and clears R. An interrupt is issued if the I bit in the BD is set. If the

next TxBD is ready, the data from its buffer is appended to the previous data and sent over

the transmit pin without any gaps between buffers. If the next TxBD is not ready, the SMC

starts sending idles and waits for the next TxBD to be ready.

By appropriately setting the I bit in each BD, interrupts can be generated after each buffer,

a speciÞc buffer, or each block is sent. The SMC then proceeds to the next BD. If the CM

bit is set in the TxBD, the R bit is not cleared, allowing a buffer to be automatically resent

next time the CP accesses this buffer. For instance, if a single TxBD is initialized with the

CM and W bits set, the buffer is sent continuously until R is cleared in the BD.

30.3.4 SMC UART Channel Reception Process

When the core enables the SMC receiver, it enters hunt mode and waits for the Þrst

character. The CP then checks the Þrst RxBD to see if it is empty and starts storing

characters in the buffer. When the buffer is full or the MAX_IDL timer expires (if enabled),

the SMC clears the E bit in the BD and generates an interrupt if the I bit in the BD is set. If

incoming data exceeds the bufferÕs length, the SMC fetches the next BD, and, if it is empty,

continues transferring data to this BDÕs buffer. If CM is set in the RxBD, the E bit is not

cleared, so the CP can overwrite this buffer on its next access.

30.3.5 Data Handling Modes: Character- and Message-Oriented

UART mode uses the same data structures as other modes. The structures support

multibuffer operation and allows break and preamble sequences to be sent. Overrun, parity,

1

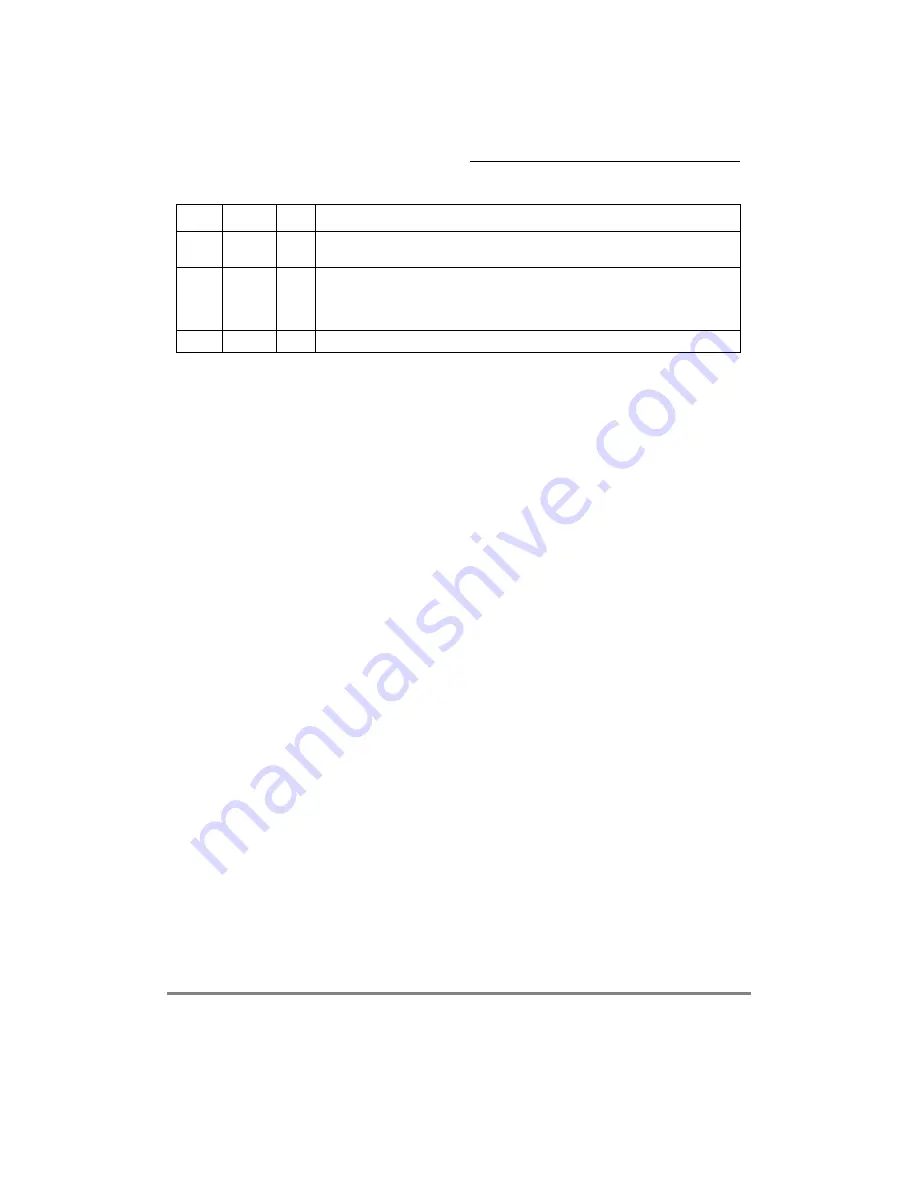

From SMC base address. SMC base = IMMR + 0x3E80 (SMC1), 0x3F80 (SMC2).

0x2E

BRKEC

Hword Receive break condition counter. Counts break conditions on the line. A break condition

may last for hundreds of bit times, yet BRKEC increments only once during that period.

0x30

BRKCR

Hword Break count register (transmit). Determines the number of break characters the UART

controller sends when the SMC sends a break character sequence after a

STOP

TRANSMIT

command. For 8 data bits, no parity, 1 stop bit, and 1 start bit, each break

character is 10 zeros.

0x32

R_MASK

Hword Temporary bit mask.

Table 30-4. SMC UART-Specific Parameter RAM Memory Map (Continued)

Offset

1

Name

Width

Description

Summary of Contents for MPC860 PowerQUICC

Page 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Page 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Page 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Page 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Page 1106: ......