16-38

MPC860 PowerQUICC UserÕs Manual

MOTOROLA

Part IV. Hardware Interface

19

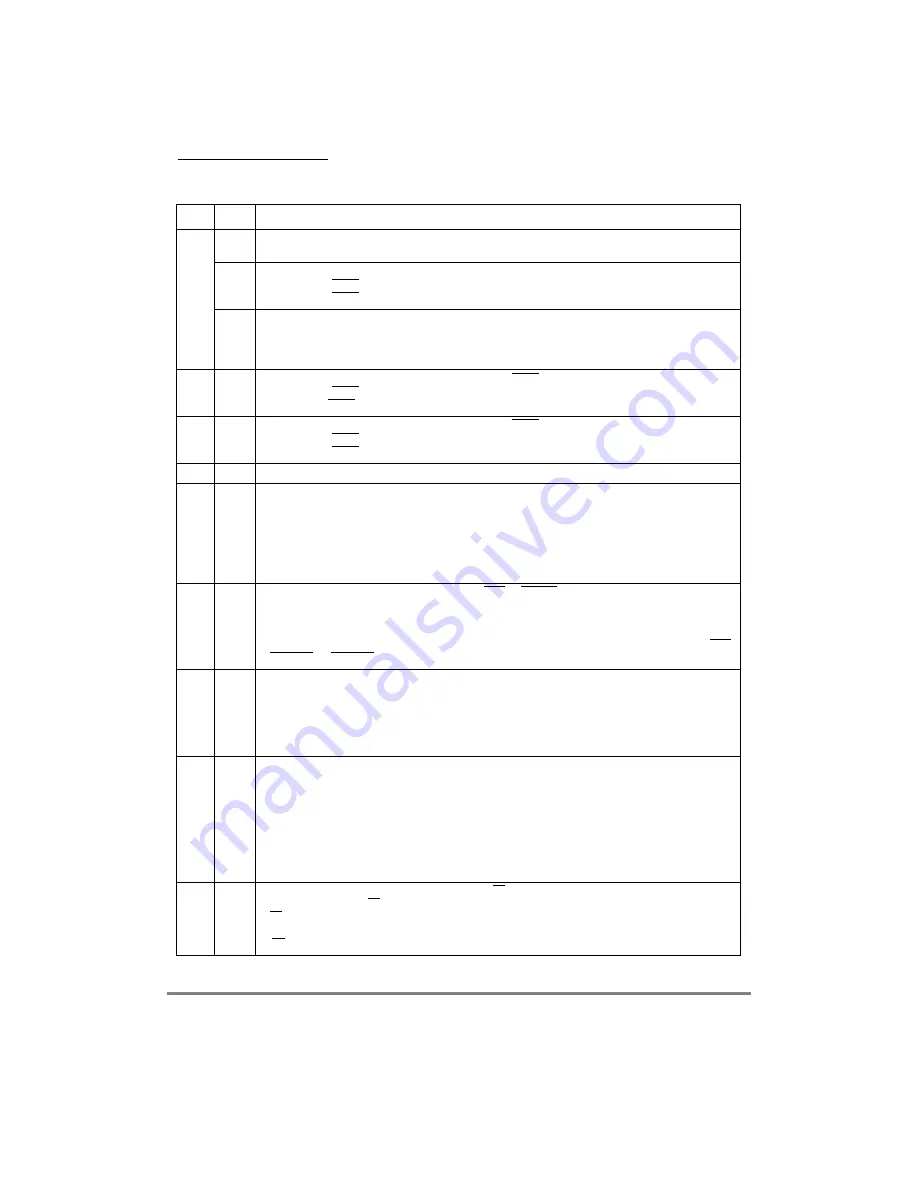

G4T3/

WAEN

General-purpose line 4 timing 3/wait enable. Function depends on the value of M

x

MR[GPL

x

4DIS].

G4T3

If M

x

MR[GPL

x

4DIS] = 0, G4T3 is selected.

0 The value of GPL4 at the falling edge of GCLK1_50 will be 0.

1 The value of GPL4 at the falling edge of GCLK1_50 will be 1.

WAEN If M

x

MR[GPL

x

4DIS] = 1, WAEN is selected.

0 The UPWAITx function is disabled.

1 The logical value of the UPM-controlled external signals are frozen when UPWAITx is asserted.

UPWAITx is sampled on the falling edge of GCLK2_50. See Figure 16-45 for more information.

20

G5T4

General-purpose line 5 timing 4. DeÞnes the state of GPL5 during phase 1Ð3.

0 The value of GPL5 at the falling edge of GCLK2_50 will be 0.

1The value of GPL5 at the falling edge of GCLK2_50 will be 1.

21

G5T3

General-purpose line 5 timing 3. DeÞnes the state of GPL5 during phase 4.

0 The value of GPL5 at the falling edge of GCLK1_50 will be 0.

1 The value of GPL5 at the falling edge of GCLK1_50 will be 1.

22Ð23

Ñ

Reserved, should be cleared.

24

LOOP Loop. The Þrst RAM word in the RAM array where LOOP is 1 is recognized as the loop start word.

The next RAM word where LOOP is 1 is the loop end word. RAM words between the start and end

are deÞned as the loop. The number of times the UPM executes this loop is deÞned in the

corresponding loop Þeld of the M

x

MR.

0 The current RAM word is not the loop start word or loop end word.

1 The current RAM word is the start or end of a loop.

See Section 16.6.4.5, ÒLoop Control (LOOP).Ó

25

EXEN Exception enable. If an external device asserts TEA or RESET, EXEN allows branching to an

exception pattern at the exception start address (EXS) at a Þxed address in the RAM array.

0 The UPM continues executing the remaining RAM words.

1 The current RAM word allows a branch to the exception pattern after the current cycle if an

exception condition is detected. The exception condition can be an external device asserting TEA,

HRESET, or SRESET.

26Ð27

AMX

Address multiplexing. Determines the source of A[0Ð31] at the falling edge of GCLK1_50.

00 A[0Ð31] is the non-multiplexed address. For example, column address.

01 Reserved.

10 A[0Ð31] is the address requested by the internal master multiplexed according to M

x

MR[AM

x

].

For example, row address.

11 A[0Ð31]

is the contents of MAR. Used for example, during SDRAM mode initialization.

28

NA

Next address. Determines when the address is incremented during a burst access.

0 The address increment function is disabled

1 The address is incremented in the next cycle. In conjunction with the BR

x

[PS], the increment value

of A[28Ð31] and/or BADDR[28Ð30] at the falling edge of GCLK1_50 is as follows

If the accessed bank has a 32-bit port size, the value is incremented by 4.

If the accessed bank has a 16-bit port size, the value is incremented by 2.

If the accessed bank has an 8-bit port size, the value is incremented by 1.

Note: The value of NA is relevant only when the UPM serves a burst-read or burst-write request. NA

is reserved under other patterns.

29

UTA

UPM transfer acknowledge. Controls the state of TA sampled by the external bus interface in the

current memory cycle. TA is output at the rising edge of GCLK2_50.

0 TA is driven low on the rising edge of GCLK2_50. The bus master samples it low in the next clock

cycle.

1 TA is driven high on the rising edge of GCLK2_50.

Table 16-13. RAM Word Bit Settings (Continued)

Bit

Name

Description

Summary of Contents for MPC860 PowerQUICC

Page 3: ...MPC860UM AD 07 98 REV 1 MPC860 PowerQUICC ª UserÕs Manual ...

Page 36: ...xxxvi MPC860 PowerQUICC UserÕs Manual MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 78: ...I iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 88: ...1 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 114: ...3 16 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part I Overview ...

Page 226: ...8 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 262: ...9 36 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part II PowerPC Microprocessor Module ...

Page 274: ...III iv MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 320: ...12 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part III Configuration ...

Page 325: ...MOTOROLA Part IV Hardware Interface IV v Part IV Hardware Interface ...

Page 326: ...IV vi MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 352: ...13 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 394: ...14 42 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 426: ...15 32 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 530: ...17 26 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part IV Hardware Interface ...

Page 632: ...21 44 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 660: ...22 28 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 708: ...24 24 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 748: ...27 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 846: ...31 20 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 914: ...35 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 948: ...36 34 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part V The Communications Processor Module ...

Page 998: ...37 48 MPC860 PowerQUICC UserÕs Manual MOTOROLA Part VI Debug and Test ...

Page 1016: ...A 10 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1024: ...B 8 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1030: ...C 6 MPC860 PowerQUICC UserÕs Manual MOTOROLA Appendixes ...

Page 1086: ...Glossary 12 MPC860 PowerQUICC UserÕs Manual MOTOROLA ...

Page 1106: ......