MATH COPROCESSING

11-10

11.4.1 Clocking the 80C187

The microprocessor and math coprocessor operate asynchronously, and their clock rates may dif-

fer. The 80C187 has a CKM pin that determines whether it uses the input clock directly or divided

by two. Direct clocking works up to 12.5 MHz, which makes it convenient to feed the clock input

from the microprocessor’s CLKOUT pin. Beyond 12.5 MHz, the 80C187 must use a multiply-

by-two clock input up to a maximum of 32 MHz. The microprocessor and the math coprocessor

have correct timing relationships, even with operation at different frequencies.

11.4.2 Processor Bus Cycles Accessing the 80C187

Data transfers between the microprocessor and the 80C187 occur through the dedicated, 16-bit

I/O ports shown in Table 11-7. When the processor encounters a numerics opcode, it first writes

the opcode to the 80C187. The 80C187 decodes the instruction and passes elementary instruction

information (Opcode Status Word) back to the processor. Since the 80C187 is a slave processor,

the Modular Core processor performs all loads and stores to memory. Including the overhead in

the microprocessor’s microcode, each data transfer between memory and the 80C187 (via the mi-

croprocessor) takes at least 17 processor clocks.

The microprocessor cannot process any numerics (ESC) opcodes alone. If the CPU encounters a

numerics opcode when the Escape Trap (ET) bit in the Relocation Register is a zero and the

80C187 is not present, its operation is indeterminate. Even the FINIT/FNINIT initialization in-

struction (used in the past to test the presence of a coprocessor) fails without the 80C187. If an

application offers the 80C187 as an option, problems can be prevented in one of three ways:

•

Remove all numerics (ESC) instructions, including code that checks for the presence of the

80C187.

•

Use a jumper or switch setting to indicate the presence of the 80C187. The program can

interrogate the jumper or switch setting and branch away from numerics instructions when

the 80C187 socket is empty.

•

Trick the microprocessor into predictable operation when the 80C187 socket is empty. The

fix is placing pull-up or pull-down resistors on certain data and handshaking lines so the

CPU reads a recognizable Opcode Status Word. This solution requires a detailed knowledge

of the interface.

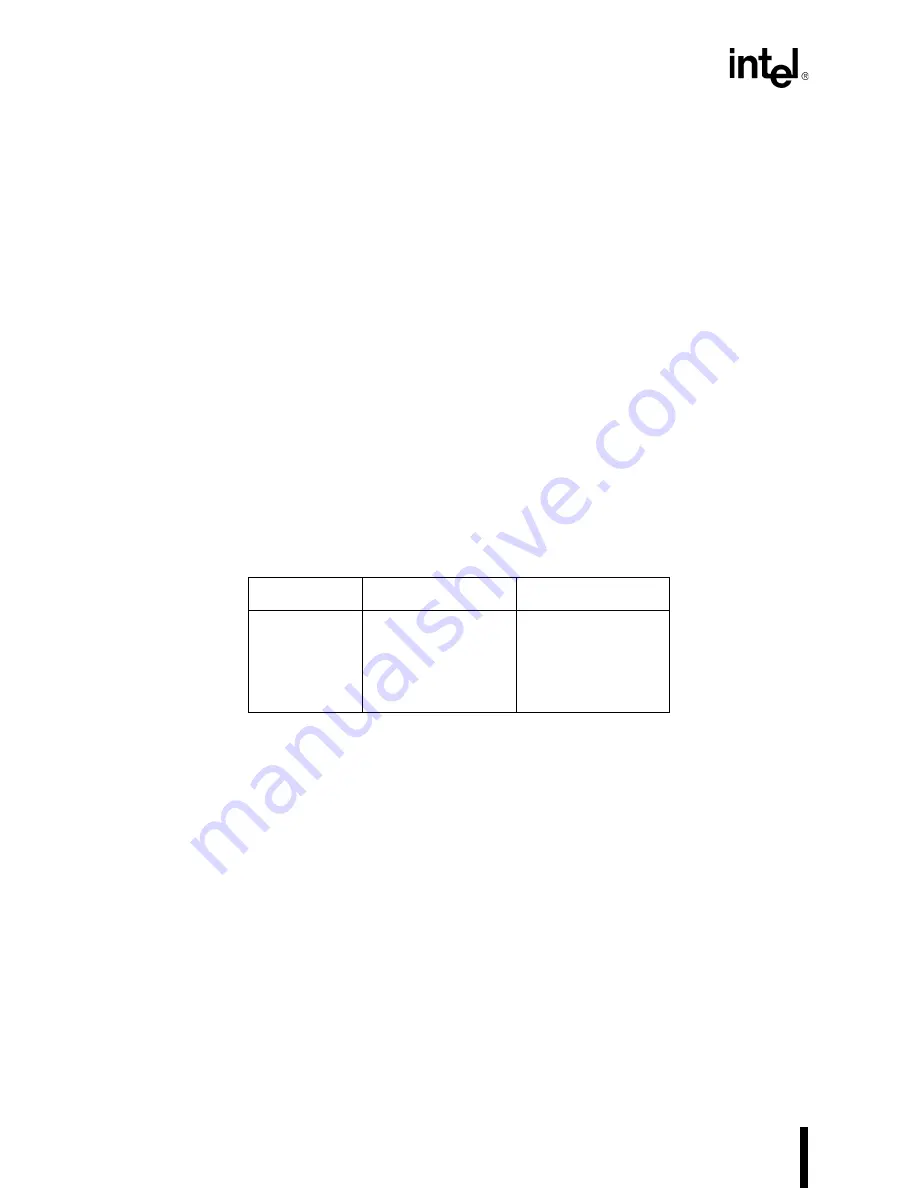

Table 11-7. 80C187 I/O Port Assignments

I/O Address

Read Definition

Write Definition

00F8H

Status/Control

Opcode

00FAH

Data

Data

00FCH

Reserved

CS:IP, DS:EA

00FEH

Opcode Status

Reserved

Summary of Contents for 80C186XL

Page 1: ...80C186XL 80C188XL Microprocessor User s Manual...

Page 2: ...80C186XL 80C188XL Microprocessor User s Manual 1995...

Page 18: ...1 Introduction...

Page 19: ......

Page 27: ......

Page 28: ...2 Overview of the 80C186 Family Architecture...

Page 29: ......

Page 79: ......

Page 80: ...3 Bus Interface Unit...

Page 81: ......

Page 127: ......

Page 128: ...4 Peripheral Control Block...

Page 129: ......

Page 137: ......

Page 138: ...5 ClockGenerationand Power Management...

Page 139: ......

Page 154: ...6 Chip Select Unit...

Page 155: ......

Page 178: ...7 Refresh Control Unit...

Page 179: ......

Page 193: ......

Page 194: ...8 Interrupt Control Unit...

Page 195: ......

Page 227: ......

Page 228: ...9 Timer Counter Unit...

Page 229: ......

Page 253: ......

Page 254: ...10 Direct Memory Access Unit...

Page 255: ......

Page 283: ......

Page 284: ...11 Math Coprocessing...

Page 285: ......

Page 302: ...12 ONCE Mode...

Page 303: ......

Page 306: ...A 80C186 Instruction Set Additions and Extensions...

Page 307: ......

Page 318: ...B Input Synchronization...

Page 319: ......

Page 322: ...C Instruction Set Descriptions...

Page 323: ......

Page 371: ......

Page 372: ...D Instruction Set Opcodes and Clock Cycles...

Page 373: ......

Page 396: ...Index...

Page 397: ......