TIMER/COUNTER UNIT

9-12

9.2.2

Clock Sources

The 16-bit Timer Count register increments once for each timer event. A timer event can be a

low-to-high transition on a timer input pin (Timers 0 and 1), a pulse generated every fourth CPU

clock (all timers) or a timeout of Timer 2 (Timers 0 and 1). Up to 65536 (2

16

) events can be count-

ed.

Timers 0 and 1 can be programmed to count low-to-high transitions on their input pins as timer

events by setting the External (EXT) bit in their control registers. Transitions on the external pin

are synchronized to the CPU clock before being presented to the timer circuitry. The timer counts

transitions on this pin. The input signal must go low, then high, to cause the timer to increment.

The maximum count-rate for the timers is ¼ the CPU clock rate (measured at CLKOUT) because

the timers are serviced only once every four clocks.

All timers can use transitions of the CPU clock as timer events. For internal clocking, the timer

increments every fourth CPU clock due to the counter element’s time-multiplexed servicing

scheme. Timer 2 can use only the internal clock as a timer event.

Timers 0 and 1 can also use Timer 2 reaching its maximum count as a timer event. In this config-

uration, Timer 0 or Timer 1 increments each time Timer 2 reaches its maximum count. See Table

9-1 for a summary of clock sources for Timers 0 and 1. Timer 2 must be initialized and running

in order to increment values in other timer/counters.

9.2.3

Counting Modes

All timers have a Timer Count register and a Maxcount Compare A register. Timers 0 and 1 also

have access to a second Maxcount Compare B register. Whenever the contents of the Timer

Count register equal the contents of the Maxcount Compare register, the count register resets to

zero. The maximum count value will never be stored in the count register. This is because the

counter element increments, compares and resets a timer in one clock cycle. Therefore, the max-

imum value is never written back to the count register. The Maxcount Compare register can be

written at any time during timer operation.

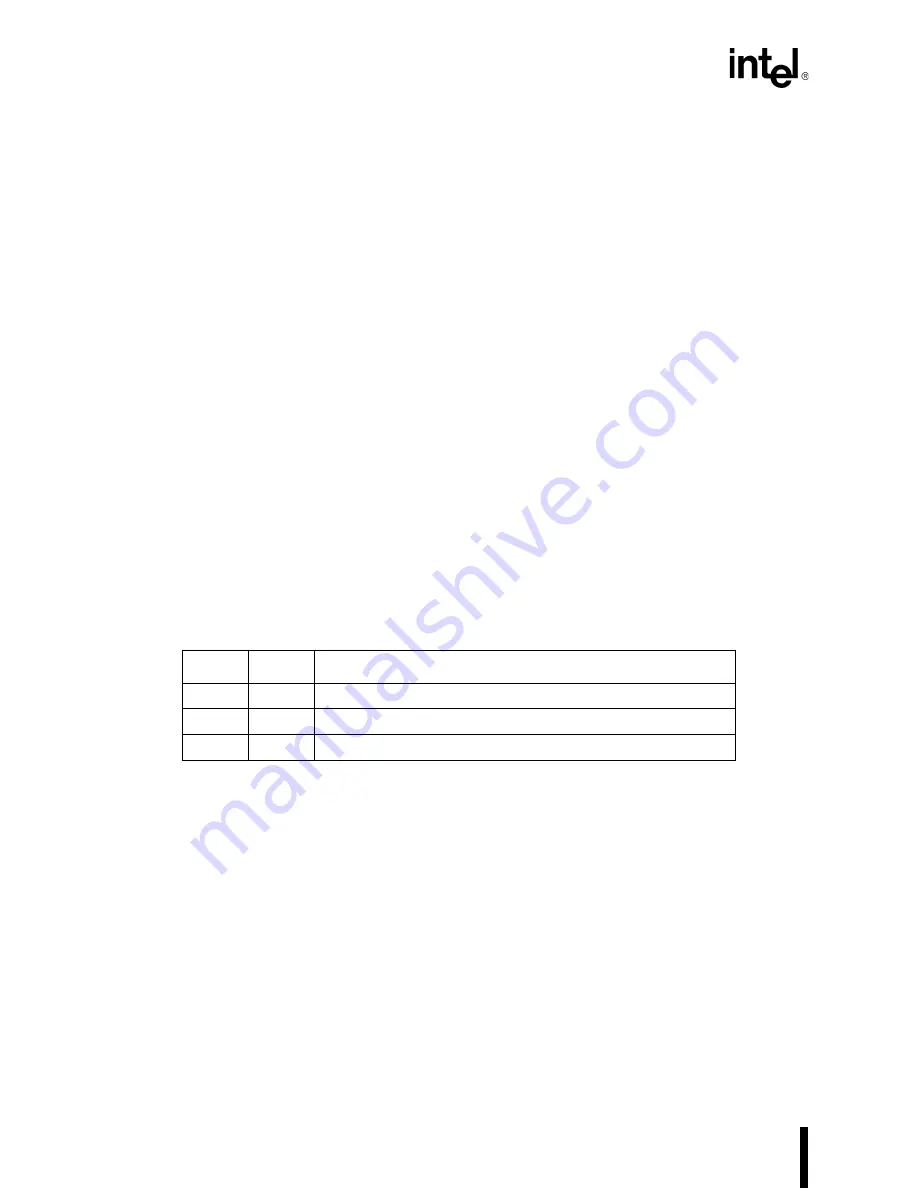

Table 9-1. Timer 0 and 1 Clock Sources

EXT

P

Clock Source

0

0

Timer clocked internally at ¼ CLKOUT frequency.

0

1

Timer clocked internally, prescaled by Timer 2.

1

X

Timer clocked externally at up to ¼ CLKOUT frequency.

Summary of Contents for 80C186XL

Page 1: ...80C186XL 80C188XL Microprocessor User s Manual...

Page 2: ...80C186XL 80C188XL Microprocessor User s Manual 1995...

Page 18: ...1 Introduction...

Page 19: ......

Page 27: ......

Page 28: ...2 Overview of the 80C186 Family Architecture...

Page 29: ......

Page 79: ......

Page 80: ...3 Bus Interface Unit...

Page 81: ......

Page 127: ......

Page 128: ...4 Peripheral Control Block...

Page 129: ......

Page 137: ......

Page 138: ...5 ClockGenerationand Power Management...

Page 139: ......

Page 154: ...6 Chip Select Unit...

Page 155: ......

Page 178: ...7 Refresh Control Unit...

Page 179: ......

Page 193: ......

Page 194: ...8 Interrupt Control Unit...

Page 195: ......

Page 227: ......

Page 228: ...9 Timer Counter Unit...

Page 229: ......

Page 253: ......

Page 254: ...10 Direct Memory Access Unit...

Page 255: ......

Page 283: ......

Page 284: ...11 Math Coprocessing...

Page 285: ......

Page 302: ...12 ONCE Mode...

Page 303: ......

Page 306: ...A 80C186 Instruction Set Additions and Extensions...

Page 307: ......

Page 318: ...B Input Synchronization...

Page 319: ......

Page 322: ...C Instruction Set Descriptions...

Page 323: ......

Page 371: ......

Page 372: ...D Instruction Set Opcodes and Clock Cycles...

Page 373: ......

Page 396: ...Index...

Page 397: ......