Altera Corporation

2–207

October 2007

Stratix II GX Device Handbook, Volume 2

Stratix II GX Transceiver Architecture Overview

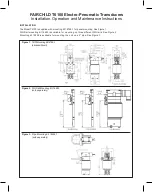

Figure 2–153. Stratix II GX Block in PCI Express PIPE Reverse Parallel Loopback Mode

Reverse Serial Loopback

Reverse serial loopback is a subprotocol in Basic mode. It requires

8B/10B, and the word aligner pattern of K28.5. No dynamic pin control is

available to select or deselect reverse serial loopback. The active block of

the transmitter is only the buffer. The data sent to the receiver is retimed

with the recovered clock and sent out to the transmitter.

The data path for reverse serial loopback is shown in

Figure 2–154

. Data

comes in from the

rx_datain

ports in the receiver. The data is then fed

through the CDR block in serial form directly to the

tx_dataout

ports

in the transmitter block.

You can enable reverse serial loopback for all channels through the

MegaWizard. Any pre-emphasis setting on the transmitter buffer is

ignored in reverse serial loopback. The data flows through the active

blocks of the receiver and into the logic array.

Reverse serial loopback is often implemented when using a bit error rate

tester (BERT).

Transmitter Digital Logic

Receiver Digital Logic

Analog Receiver and

Transmitter Logic

FPGA

Logic

Array

BIST

Incremental

Generator

TX Phase

Compensation

FIFO

RX Phase

Compen-

sation

FIFO

Byte

Serializer

8B/10B

Encoder

Serializer

BIST

PRBS

Verify

Clock

Recovery

Unit

Word

Aligner

Deskew

FIFO

8B/10B

Decoder

Byte

De-

serializer

Byte

Ordering

BIST

Incremental

Verify

Rate

Match

FIFO

De-

serializer

BIST

PRBS

Generator

20

PCI Express PIPE

Reverse Parallel

Loopback