Altera Corporation

2–13

October 2007

Stratix II GX Device Handbook, Volume 2

Stratix II GX Transceiver Architecture Overview

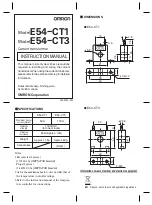

Figure 2–4

shows the transmitter PLL block.

Figure 2–4. Transmitter PLL Block

Note to

Figure 2–4

:

(1)

The Global Clock line must be driven by an input pin.

Transmitter PLLs

There are two transmitter PLLs in each CMU (transmitter PLL0 and

transmitter PLL1). Transmitter PLL0 and transmitter PLL1 receive the

reference clock from one of five inter-transceiver lines (refer to

“Inter-Transceiver Line Routing” on page 2–19

for more information), a

global PLD clock driven from a clock input pin, or from the dedicated

reference clock

REFCLK0

or

REFCLK1

(both reference clock pins can drive

either transmitter PLL0 or transmitter PLL1). You can divide the reference

clocks from the

REFCLK

pins by two to support higher reference clock

frequencies.

Transmitter PLL0 and transmitter PLL1 have half-rate VCOs that operate

at half the rate of the serial data stream. The range of these VCOs are from

500 MHz to 3.1875 GHz to support a native data rate of 1 Gbps to

6.375 GHz. Lower data rates (600 Mbps to 1 Gbps) are supported via

additional clock dividers (refer to

“Clock Synthesis” on page 2–16

for

more information).

PFD

Dedicated Local

REFCLK 0

CP+LF

up

dn

VCO

m

High-Speed

Transmitter PLL Clock

Inter-Transceiver Block

Routing (IQ[4..0])

Inter-Transceiver Block

Routing (IQ[4..0])

INCLK

L

PFD

Dedicated Local

REFCLK 1

CP+LF

up

dn

VCO

m

2

INCLK

L

Transmitter PLL 1

Transmitter PLL 0

High-Speed

Transmitter PLL0 Clock

High-Speed

Transmitter PLL1 Clock

To Inter-Transceiver

Block Line

/2

2

÷

÷

÷

÷

÷

÷

From Global Clock

(1)