Chapter 23 Notes on Use of TMPR4937

23-7

<Conditions>

This problem occurs when the following conditions are satisfied.

(1) The broken master detection function is enabled (BMCEN=1).

The broken master detection function is enabled or disabled with the BMCEN bit of the PCI bus

arbiter configuration register (PBACFG). The default value is 0 which disables the function.

(2) The bus masters are assigned to the high level and low level in the on-chip PCI bus arbiter.

The bus master is assigned to the bus arbiter with the PCI Bus Arbiter Request Port Register

(PBAREQPORT).

(3) When the PCI bus master connected to the high level is detected as the broken master, the master

connected to the low level requests the bus mastership, which is the highest-priority request in the

low level. (That is Master W immediately after a reset or the master which acquires the bus

mastership most recently in the low level when the fixed park master mode is not set, or Master W

that is the park master in the fixed park master mode.)

PCI Arbitration Priority

[Workarounds]

There are two workarounds for this problem.

(1) Don’t use the broken master function.

Don’t set the BMCEN bit of the PBACFG register.

(2) When using the broken master function, use only the high level containing Master A, B, C and D.

Low Level

(Priority: Low)

High Level

(Priority: High)

Master A

Low-level

Master

Master Z

Master X

(Park master)

Master W

Master B

Master C

Master D

Master Y

PCI Bus Master 1

PCI Bus Master 2

Request

Request

Grant

Access is not started

within 16PCICLK

Broken Master

PCI bus master 2

also becomes a

broken master.

On-chip PCI Controller

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

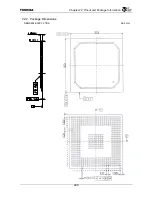

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...