Chapter 11 Serial I/O Port

11-11

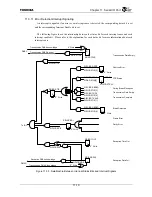

11.3.12 Multi-Controller System

The Multi-Controller System consists of one Master Controller, and multiple Slave Controllers as

shown below in Figure 11.3.4.

In the case of the Multi-Controller System, the Master Controller transmits an address (ID) frame to

all Slave Controllers, then transmits and receives data with the selected Slave Controller. Slave

Controllers that were not selected will ignore this data.

Data frames whose data frame Wake Up bits (WUB) are “1” are handled as address (ID) frames. Data

frames whose Wake Up bit (WUB) is “0” are handled as data frames.

Figure 11.3.4 Example Configuration of Multi-Controller System

The data transfer procedure for the Multi-Controller System is as follows.

(1) The Master and Slave Controllers set the Mode field (UMODE) of the Line Control Register

(SILCR) to “10” or “11” to set the Multi-Controller System mode. Also, the Slave Controller sets

the open drain enable bit (UODE) of the Line Control Register (SILCR), setting the TXD output

signal to open drain output.

(2) The Slave Controller sets the Reception Wake Up bit (RWUB) of the Line Control Register

(SILCR), making it possible to receive address (ID) frames from the Master Controller.

(3) The Master Controller sets the Transmission Wake Up bit (TWUB) of the Line Control Register

(SILCR), and transmits the address (ID) of the selected Slave Controller. This causes the address

(ID) frame to be transmitted. The Reception after Address Transmission Wake Up bit (RWUB) is

cleared, enabling reception of data frames.

(4) Since the Reception Wake Up bit (RWUB) is set, the Slave Controller generates an interrupt to the

CPU by receiving an address (ID) frame. The CPU compares its own address (ID) and the received

data together. If they do not match, the Reception Wake Up bit (RWUB) is cleared, making data

frame reception possible.

(5) The Master Controller and the selected Slave Controller clear the Transmission Wake Up bit

(TWUB) of the Line Control Register (SILCR), then set the mode that transmits data frames.

(6) Transmit/Receive data between the Master Controller and the selected Slave Controller. Then,

Slave Controllers that were not selected ignore data frames since the Reception Wake Up bit

(RWUB) is still set.

RXD TXD

Slave #3

RXD TXD

Slave #2

RXD TXD

Slave #1

Master

TXD RXD

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...