Appendix A TX49/H3 Core Supplement

A-1

Appendix A TX49/H3 Core Supplement

This section explains items that are unique to the TX4937 of the TX49/H3 Core. Please refer to the “64-bit

TX System RISC TX49/H2, TX49/H3, TX49/H4 Core Architecture” for more information regarding the

TX49/H3 Core.

A.1 Processor

ID

PRId Register values of the TX4937 TX49/H3 Core are as follows.

Processor Revision Identifier Register: 0x0000 2D30

FPU Implementation/Revision Register (FCR0): 0x0000 2D30

These values may be changed at a later date. Please contact the Toshiba Engineering Department for the

most recent information.

A.2 Interrupts

Interrupt signalling of the on-chip interrupt controller is reflected in bit IP[2] of the Cause Register in the

TX49/H3 Core. In addition, interrupt causes are reflected in other bits of the IP field. Please refer to Section

“15.3.5 Interrupt signalling” for more information.

A.3 Bus

Snoop

The Bus Snoop function is not used with the TX4937 due to restrictions of the Bus Snoop specification.

A.4 Halt/Doze

mode

The Doze mode is not necessary when the Bus Snoop function is not used. Please use the Halt mode,

which further reduces power consumption. Clearing the HALT bit of the Config Register makes it possible to

shift to the Halt mode by executing the WAIT instruction.

A.5

Memory access order

The TX49/H3 Core has a 4-stage Write buffer, the PCI Bus Bridge (PCI Controller) has 4 stages for

initiator access, and has a 2-stage Post Write buffer (Write buffer) for target access.

When data enters the Write buffer of the TX49/H3 Core, Cache Refill Read operations that do not match

the address of that data after the Write is issued may be issued to the internal bus (G-Bus) before the Write.

Other accesses are issued in order.

Executing the SYNC instruction guarantees that bus access invoked by a load/store instruction previously

executed will be complete on the internal bus.

The PCI Bus Bridge is issued by the issue destination bus in the order all bus accesses are issued on the

issue source bus. Please refer to “10.3.6 Post Write Function” for more information regarding methods for

guaranteeing the completion of Write transactions of the Post Write Buffer.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

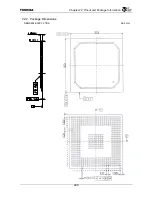

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...