Chapter 9 SDRAM Controller

9-18

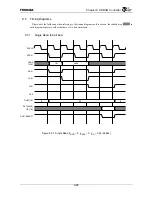

9.4.1

SDRAM Channel Control Register (SDCCRn) 0x8000 (ch. 0)

0x8008 (ch. 1)

0x8010 (ch. 2)

0x8018 (ch. 3)

When the SDCCRn is programmed using a sequence of 32-bit store instructions, the base address and

the address mask in the high-order 32-bit portion of the register must be written first, followed by the

Channel Enable bit in the low-order 32-bit portion.

63

49

48

BA

Reserved

R/W

:Type

0x01FC/0x0000

:Initial

value

47

33

32

AM

Reserved

R/W

:Type

0x0000

:Initial

value

31 29

28 16

ECC

Reserved

R/W

:Type

0 0 0

:Initial

value

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RD MT

Reserved

ME SE CE

Reserved

BS

Reserved

RS CS

Reserved

MW

R/W R/W R/W R/W R/W R/W

R/W

R/W

R/W :Type

0 0

1)

0 0 0

1)

0

000

1)

000

1)

1

:Initial

value

Bit Mnemonic Field

Name

Description

Read/Write

63:49

BA[35:21]

Base Address

Base Address (Default: 0x01FC/0x0000)

Specifies the base address. The upper 15 bits [35:21] of the physical

address are compared to the value of this field.

(Note) Only the default for Channel 0 differs. Channel 0: 0x01FC, Others:

0x0000

R/W

48 —

— Reserved

⎯

47:33

AM[35:21]

Address Mask

Address Mask (Default: 0x0000)

Sets the valid bits for address comparison according to the base address.

0: Bits of the corresponding BA field are compared.

1: Bits of the corresponding BA field are not compared.

R/W

32 —

— Reserved

⎯

31:29

ECC

ECC/Parity Mode ECC/Parity mode (Default: 000)

Specifies the channel ECC/Parity type (refer to 9.3.10.1).

000: NOP Mode

001: EC Mode

010: ECC Mode

011: ECC + scrub Mode

100: Even Parity Mode

101: Odd Parity Mode

110: Reserved

110: Reserved

R/W

28:16 —

— Reserved

⎯

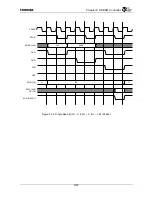

Figure 9.4.1 SDRAM Channel Control Register (1/2)

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...