Chapter 8 DMA Controller

8-6

•

When edge detection is set (DMCCRn.EGREQ

=

1)

Please set up assertion of the DMAREQ[n] signal so the DMAREQ[n] signal is asserted

after the DMAACK[n] signal corresponding to a previously asserted DMAREQ[n] signal is

deasserted. The DMAREQ[n] signal will not be detected even if it is asserted before

DMAACK[n] is deasserted.

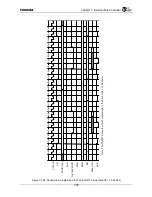

Figure 8.3.1 is a timing diagram that shows the timing of external DMA access. In this timing

diagram, both the DMAREQ[n] signal and the DMAACK[n] signal are set to Low active

(DMCCRn.REQPL = 0, DMCCRn.ACKPOL = 0).

The DMAACK[n] and DMADONE[n] signals, which are DMA control signals, are

synchronized to SDCLK. When these signals are used by an external I/O device that is

synchronous to SYSCLK, it is necessary to take clock skew into account.

The DMAACK[n] signal is asserted either at the SYSCLK cycle, the same as with assertion of

the CE*/CS* signal, or before that. In addition, it is deasserted after the last ACK*/READY signal

is deasserted.

When the DMADONE* signal (refer to 8.3.3.4) is used as an output signal, it is asserted for at

least one SYSCLK cycle while the DMAACK[n] signal is asserted either during the same

SYSCLK cycle that the CE*/CS* signal is deasserted or during a subsequent SYSCLK cycle.

When the DMADONE* signal is used as an input signal, it must be asserted for one SYSCLK

cycle while the DMAACK[n] signal is being asserted.

Figure 8.3.1 External I/O DMA Transfer (Single Address, Level Request)

1c040

SYSCLK

CE

*

ADDR [19:0]

ACE

*

OE

*

/BUSSPRT

*

SWE

*

BWE

*

DATA [31:0]

ACK

*

DMAREQ[n]

DMAACK[n]

DMADONE

*

00040

f

00000100

1 cycle

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...