Chapter 21 Electrical Characteristics

21-13

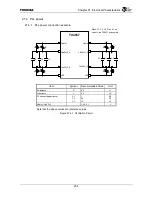

21.5.10 SIO Interface AC characteristics

(Tc

= 0 – 70

°

C, V

CCIO

= 3.3 V

±

0.2 V, V

CCInt

= 1.5 V

±

0.1 V, V

SS

= 0 V)

Item Symbol Conditions

Min. Max. Unit

Boot configuration

ADDR[2]=H

4

×

t

MCP

×

1.1

⎯

ns

SCLK Cycle time

f

CYC_SCLK

Boot configuration

ADDR[2]=L

t

MCP

×

1.1

⎯

ns

Boot configuration

ADDR[2]=H

⎯

1/2

×

f

MCK

×

0.45

MHz

SCLK Frequency

f

SCLK

Boot configuration

ADDR[2]=L

⎯

2

×

f

MCK

×

0.45

MHz

Boot configuration

ADDR[2]=H

2

×

t

MCP

×

1.1

⎯

ns

SCLK High Time

t

HIGH_SCLK

Boot configuration

ADDR[2]=L

1/2

×

t

MCP

×

1.1

⎯

ns

Boot configuration

ADDR[2]=H

2

×

t

MCP

×

1.1

⎯

ns

SCLK Low Time

t

LOW_SCLK

Boot configuration

ADDR[2]=L

1/2

×

t

MCP

×

1.1

⎯

ns

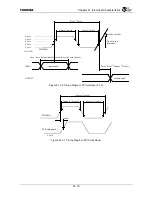

Figure 21.5.11 Timing Diagram: SIO Interface

21.5.11 Timer Interface AC characteristics

(Tc

= 0 – 70

°

C, V

CCIO

= 3.3 V

±

0.2 V, V

CCInt

= 1.5 V

±

0.1 V, V

SS

= 0 V)

Item Symbol Conditions

Min. Max. Unit

Boot configuration

ADDR[2]=H

4

×

t

MCP

×

1.1

⎯

ns

TCLK Cycle Time

f

CYC_TCLK

Boot configuration

ADDR[2]=L

t

MCP

×

1.1

⎯

ns

Boot configuration

ADDR[2]=H

⎯

1/2

×

f

MCK

×

0.45

MHz

TCLK Frequency

f

TCLK

Boot configuration

ADDR[2]=L

⎯

2

×

f

MCK

×

0.45

MHz

Boot configuration

ADDR[2]=H

2

×

t

MCP

×

1.1

⎯

ns

TCLK High Time

t

HIGH_TCLK

Boot configuration

ADDR[2]=L

1/2

×

t

MCP

×

1.1

⎯

ns

Boot Configuration

ADDR[2]=H

2

×

t

MCP

×

1.1

⎯

ns

TCLK Low Time

t

LOW_TCLK

Boot configuration

ADDR[2]=L

1/2

×

t

MCP

×

1.1

⎯

ns

Figure 21.5.12 Timing Diagram: Timer Interface

t

HIGH_SCLK

SCLK

t

LOW_SCLK

t

CYC_SCLK

/f

SCLK

t

HIGH_TCLK

TCLK

t

LOW_TCLK

t

CYC_TCLK

/f

TCLK

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

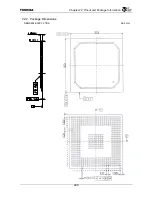

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...