Chapter 15 Interrupt Controller

15-12

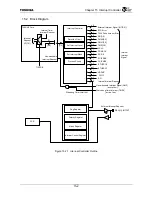

15.4.2 Interrupt Detection Mode Register 0 (IRDM0) 0xF604

31 30 29 28 27 24 23 22 21 20 19 18 17 16

IC23 IC22 IC21

Reserved

IC19 IC18 IC17 IC16

R/W R/W R/W R/W R/W R/W R/W

:

Type

0 0 0 0 0 0 0

:

Default

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

IC7 IC6 IC5 IC4 IC3 IC2 IC1 IC0

R/W R/W R/W R/W R/W R/W R/W R/W

:

Type

0 0 0 0 0 0 0 0

:

Default

Bits Mnemonic Field

Name

Explanation

Read/Write

31:30 IC23 Interrupt Source

Control 23

Interrupt Source Control 23 (Default: 00)

These bits specify the active state of PCIPMC interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

29:28 IC22 Interrupt Source

Control 22

Interrupt Source Control 22 (Default: 00)

These bits specify the active state of PCIERR0 interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

27:26 IC21 Interrupt Source

Control 21

Interrupt Source Control 21 (Default: 00)

These bits specify the active state of NDFMC interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

25:24

⎯

⎯

Reserved

⎯

23:22 IC19 Interrupt Source

Control 19

Interrupt Source Control 19 (Default: 00)

These bits specify the active state of TMR[2] interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

21:20 IC18 Interrupt Source

Control 18

Interrupt Source Control 18 (Default: 00)

These bits specify the active state of TMR[1] interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

19:18 IC17 Interrupt Source

Control 17

Interrupt Source Control 17 (Default: 00)

These bits specify the active state of TMR[0] interrupts.

00: Low level active

01: Disable

10: Disable

11: Disable

R/W

Figure 15.4.2 Interrupt Detection Mode Register 0 (1/2)

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...