Chapter 8 DMA Controller

8-5

8.3.2 On-chip

Registers

The DMA Controller has two shared registers that are shared by four channels. Section 8.4 explains

each register in detail.

•

Shared Registers

DMMCR:

DMA Master Control Register

DMMFDR:

DMA Memory Fill Data Register

•

DMA Channel Register

DMCHARn: DMA Chained Address Register

DMSARn:

DMA Source Address Register

DMDARn: DMA

Destination

Address

Register

DMCNTRn: DMA

Count

Register

DMSAIRn:

DMA Source Address Increment Register

DMDAIRn:

DMA Destination Address Increment Register

DMCCRn:

DMA Channel Control Register

DMCSRn:

DMA Channel Status Register

8.3.3

External I/O DMA Transfer Mode

The External I/O DMA Transfer Mode performs DMA transfer with external I/O devices that are

connected to the External Bus Controller.

8.3.3.1 External

Interface

External I/O devices signal DMA requests to the DMA Controller by asserting the DMA

Transfer Request Signal (DMAREQ[n]). On the other hand, the DMA Controller accesses external

I/O devices by asserting the DMA Transfer Acknowledge Signal (DMAACK[n]).

The DMA Transfer Request signal (DMAREQ[n]) can use the Request Polarity bit (REQPOL)

of the DMA Channel Control Register (DMCCRn) to select the signal polarity for each channel,

and can use the Edge Request bit (EGREQ) to select either edge detection or level detection for

each channel. The DMA Transfer Acknowledge signal (DMAACK[n]) can also use the

Acknowledge Polarity bit (ACKPOL) to select the polarity.

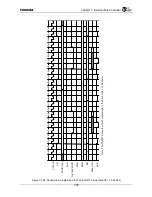

Please assert/deassert the DMAREQ[n] signal as follows below.

•

When level detection is set (DMCCRn.EGREQ = 0)

The DMAREQ[n] signal must be continuously asserted until one SYSCLK cycle after the

DMAACK[n] signal is asserted. Also, the DMAREQ[n] signal must be deasserted before the

CE*/CS* signal is deasserted. If this signal is asserted too soon, DMA transfer will not be

performed. If this signal is asserted or deasserted too late, unexpected DMA transfer may

result.

During Dual Address transfer, we recommend detecting assertion of the CE* signal for the

external I/O device that is currently asserting DMAACK[n], then deasserting DMAREQ[n].

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...