Chapter 15 Interrupt Controller

15-9

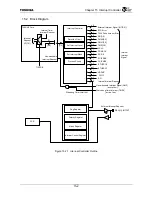

There are two flag registers: Flag Register 0 (IRFLAG0), and Flag Register 1 (IRFLAG1). These

registers have two different Write methods. Accordingly, Writes to one register are reflects in the other.

Either “0” or “1” can be written to Flag Register 0

In the case of Flag Register 1 however, “1” can be written from the TX49/H3 core, but “0” cannot be

written. On the other hand, bits that wrote “1” are cleared to “0” in the case of access from a device

other than the TX49/H3 core (access from an external PCI device for example). The bit value at this

time will not change even if “0” is written. This register sends interrupt notification from the TX49/H3

core to external devices. External devices can be used in applications that clear these interrupt

notifications.

Summary of Contents for TX49 TMPR4937

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4937 Rev 2 0 ...

Page 4: ......

Page 13: ...Table of Contents ix TMPR4937 Revision History 1 ...

Page 14: ...Table of Contents x ...

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4937 2005 3 Rev 2 0 ...

Page 44: ......

Page 52: ...Chapter 1 Overview and Features 1 6 ...

Page 156: ...Chapter 7 External Bus Controller 7 56 ...

Page 491: ...Chapter 16 Removed 16 1 16 Removed ...

Page 492: ...Chapter 16 Removed 16 2 ...

Page 493: ...Chapter 17 Removed 17 1 17 Removed ...

Page 494: ...Chapter 17 Removed 17 2 ...

Page 495: ...Chapter 18 Removed 18 1 18 Removed ...

Page 496: ...Chapter 18 Removed 18 2 ...

Page 497: ...Chapter 19 Removed 19 1 19 Removed ...

Page 498: ...Chapter 19 Removed 19 2 ...

Page 506: ...Chapter 20 Extended EJTAG Interface 20 8 ...

Page 530: ...Chapter 22 Pinout and Package Information 22 10 ...

Page 542: ...Chapter 24 Parts Number when Ordering 24 2 ...