829

Chapter 27

Electrical Specification

User’s Manual U16702EE3V2UD00

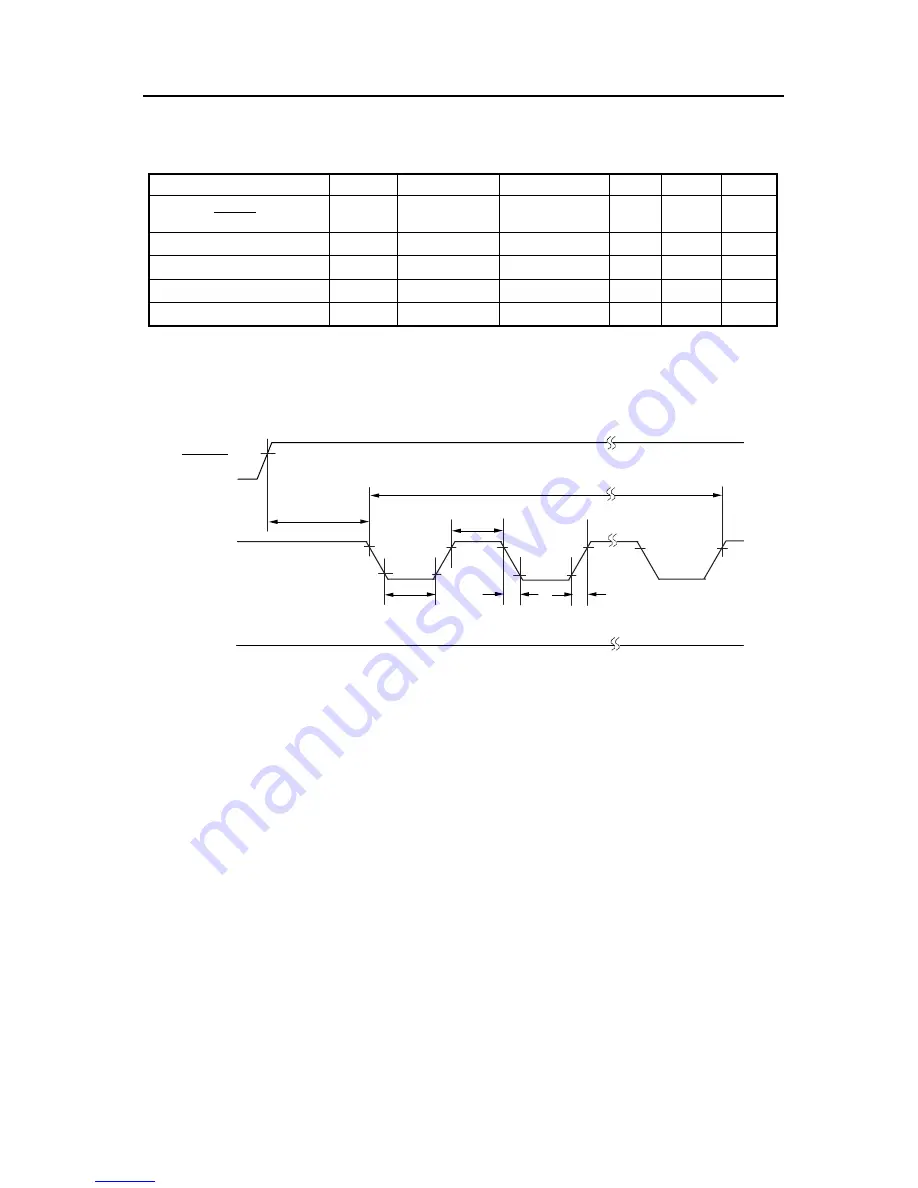

27.10.4 External Flash programmer serial write operation characteristics

Note:

α

= oscillation stabilization time

Figure 27-17:

Flash EPROM Serial Programming Operation Characteristics

Parameter

Symbol

Conditions

MIN.

TYP.

MAX.

Unit

FLMD0 setup time (from

release of RESET signal)

t

RFCF

16581/f

X

+

α

Note

-

-

s

FLMD0 high level width

t

CH

10

-

100

µs

FLMD0 low level width

t

CL

10

-

100

µs

FLMD0 rise time

t

RF

-

-

50

ns

FLMD0 fall time

t

F

-

-

50

ns

t

RFCF

RESET

t

CH

FLMD0

FLMD1

L

t

COUNT

t

CL

t

F

t

R

electronic components distributor