. . . . .

W O R K I N G W I T H T H E C P U

R13:Process ID register

www.digiembedded.com

103

Use the Process ID register to determine the process that is currently running. The

process identifier is set to 0 at reset.

FCSE PID

register

Addresses issued by the ARM926EJ-S core, in the range 0 to 32 MB, are translated

according to the value contained in the FCSE PID register. Address A becomes

A + (FCSE PID x 32 MB)

; it is this modified address that the MMU and caches see.

Addresses above 32 MB are not modified. The FCSE PID is a 7-bit field, which allows

128 x 32 MB processes to be mapped.

If the FCSE PID is 0, there is a flat mapping between the virtual addresses output by

the ARM926EJ-S core and the modified virtual addresses used by the caches and

MMU. The FCSE PID is set to 0 at system reset.

If the MMU is disabled, there is no FCSE address translation.

FCSE translation is not applied for addresses used for entry-based cache or TLB

maintenance operations. For these operations,

VA=MVA

.

Access

instructions

Use these instructions to access the FCSE PID register:

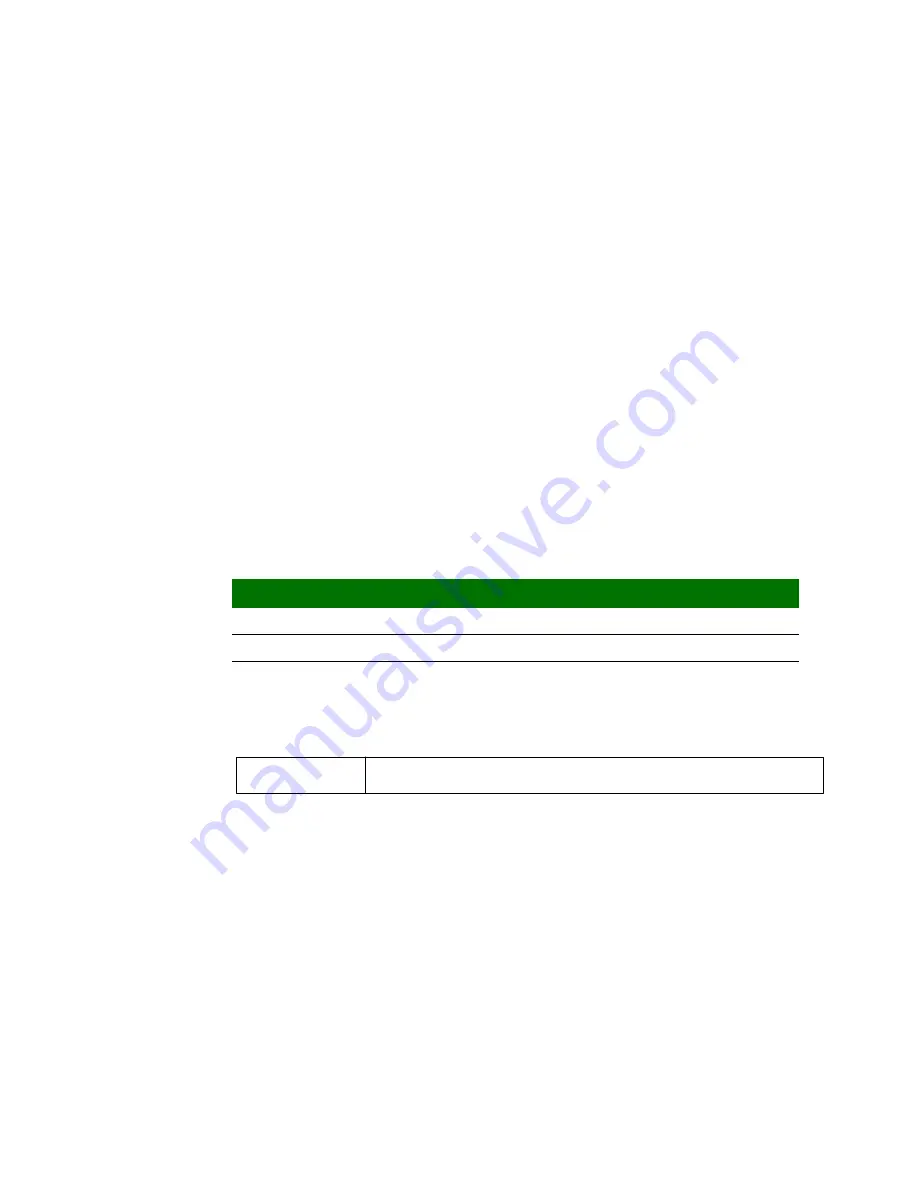

Register format

This is the format of the FCSE PID register.

Performing a fast

context switch

You can perform a fast context switch by writing to the Process ID register (R13)

with

opcode_2

set to 0. The contents of the caches and the TLB do not have to be

flushed after a fast context switch because they still hold address tags. The two

instructions after the FCSE PID has been written have been fetched with the old

FCSE PID, as shown in this code example:

{FCSE PID = 0}

MOV r0, #1:SHL:25

;Fetched with FCSE PID = 0

MCR p15,0,r0,c13,c0,0

;Fetched with FCSE PID = 0

A1

;Fetched with FCSE PID = 0

A2

;Fetched with FCSE PID = 0

A3

;Fetched with FCSE PID = 1

opcode_2=1

Selects the context ID register.

Function

Data

ARM instruction

Read FCSE PID

FCSE PID

MRC p15,0,Rd,c13,c0,0

Write FCSE PID

FCSE PID

MCR p15,0,Rd,c13,c0,0

31

25 24

0

SBZ

FCSE PID

Summary of Contents for NS9215

Page 1: ...NS9215 Hardware Reference 90000847_C Release date 10 April 2008...

Page 3: ......

Page 4: ......

Page 26: ...26 Hardware Reference NS9215...

Page 44: ...P I N O U T 26 5 System clock 44 Hardware Reference NS9215 System clock drawing...

Page 52: ...P I N O U T 26 5 Power and ground 52 Hardware Reference NS9215...

Page 80: ...I O C O N T ROL M O D U L E Memory Bus Configuration register 80 Hardware Reference NS9215...

Page 136: ...WOR KI N G W I TH T H E C P U Noncachable instruction fetches 136 Hardware Reference NS9215...

Page 202: ...S Y S T E M C O N T RO L M OD U L E RTC Module Control register 202 Hardware Reference NS9215...

Page 354: ...E X T E R N A L D M A DMA Peripheral Chip Select register 354 Hardware Reference NS9215...

Page 472: ...R E A L TI M E C L O C K M O D U L E General Status register 472 Hardware Reference NS9215...

Page 512: ...TI M I NG Clock timing 512 Hardware Reference NS9215...

Page 515: ...PA CKA GING Processor Dimensions www digiembedded com 515...

Page 516: ...PA CKA GING Processor Dimensions 516 Hardware Reference NS9215...