344

12.3.2

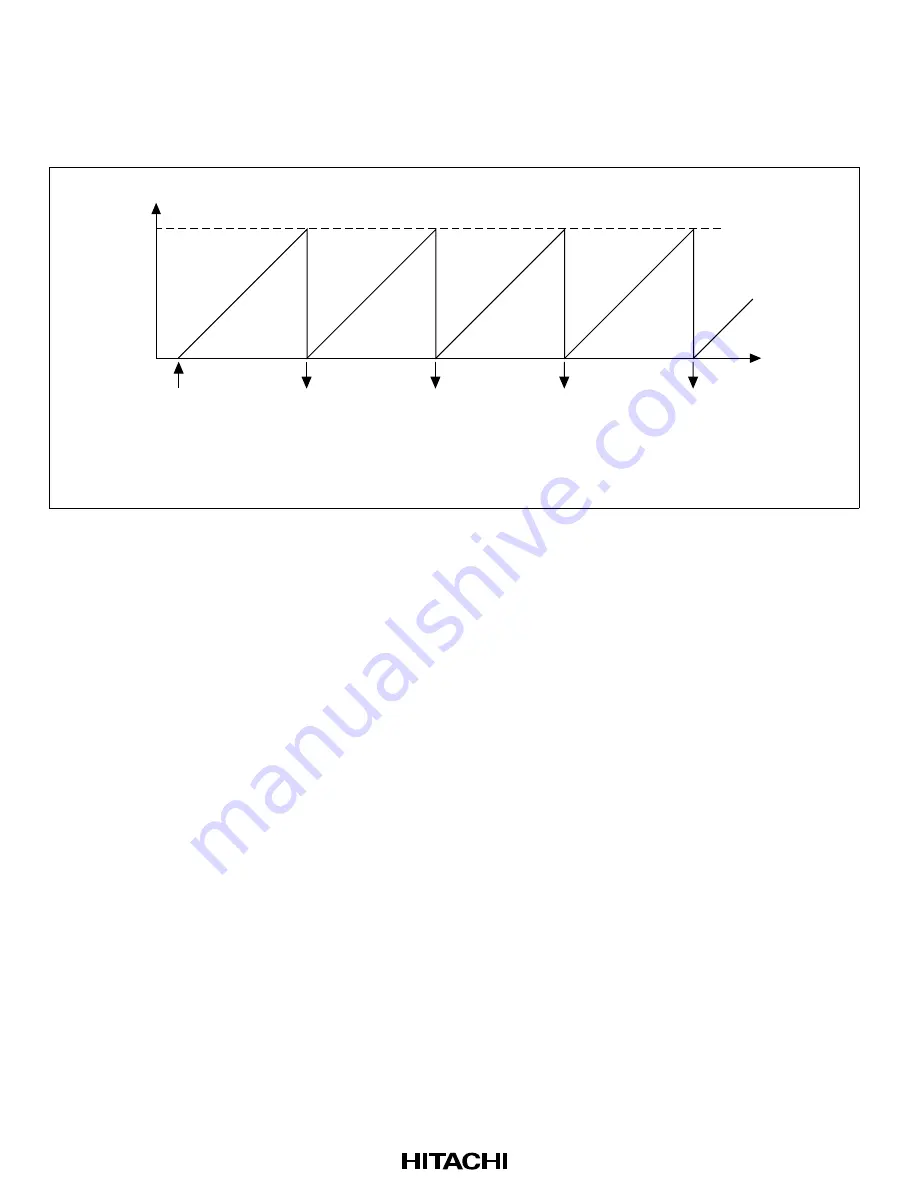

Operation in Interval Timer Mode

To use the WDT as an interval timer, clear WT/

IT

to 0 and set TME to 1. An interval timer

interrupt (ITI) is generated each time the timer counter overflows. This function can be used to

generate interval timer interrupts at regular intervals (figure 12.5).

H'FF

TCNT value

H'00

WT/

IT

= 0

TME = 1

IT I

IT I

IT I

IT I

Time

Overflow

Overflow

Overflow

Overflow

ITI: Interval timer interrupt request

Figure 12.5 Operation in Interval Timer Mode

12.3.3

Operation in Standby Mode

The watchdog timer has a special function to clear standby mode with an NMI interrupt. When

using standby mode, set the WDT as described below.

Transition to Standby Mode: The TME bit in TCSR must be cleared to 0 to stop the watchdog

timer counter before it enters standby mode. The chip cannot enter standby mode while the TME

bit is set to 1. Set bits CKS2–CKS0 so that the counter overflow interval is equal to or longer than

the oscillation settling time. See sections 20.1.3 and 20.2.3, AC Characteristics, for the oscillation

settling time.

Recovery from Standby Mode: When an NMI request signal is received in standby mode, the

clock oscillator starts running and the watchdog timer starts counting at the rate selected by bits

CKS2–CKS0 before standby mode was entered. When TCNT overflows (changes from H'FF to

H'00), the system clock (

φ

) is presumed to be stable and usable; clock signals are supplied to the

entire chip and standby mode ends.

For details on standby mode, see section 19, Power Down State.

Summary of Contents for HD6417032

Page 21: ......

Page 35: ...xiv ...

Page 85: ...50 ...

Page 101: ...66 ...

Page 129: ...94 ...

Page 135: ...100 ...

Page 343: ...308 ...

Page 369: ...334 ...

Page 383: ...348 ...

Page 475: ...440 ...

Page 525: ...490 CK RAS CAS TRp TRc TRcc tRASD1 tRASD2 tCASD3 tCASD2 TRr tCSR Figure 20 18 Self Refresh ...

Page 578: ...543 CK RAS CAS TRp TRc TRcc tRASD1 tRASD2 tCASD3 tCASD2 TRr tCSR Figure 20 62 Self Refresh ...

Page 689: ...654 ...