Acronyms

RM0082

Doc ID 018672 Rev 1

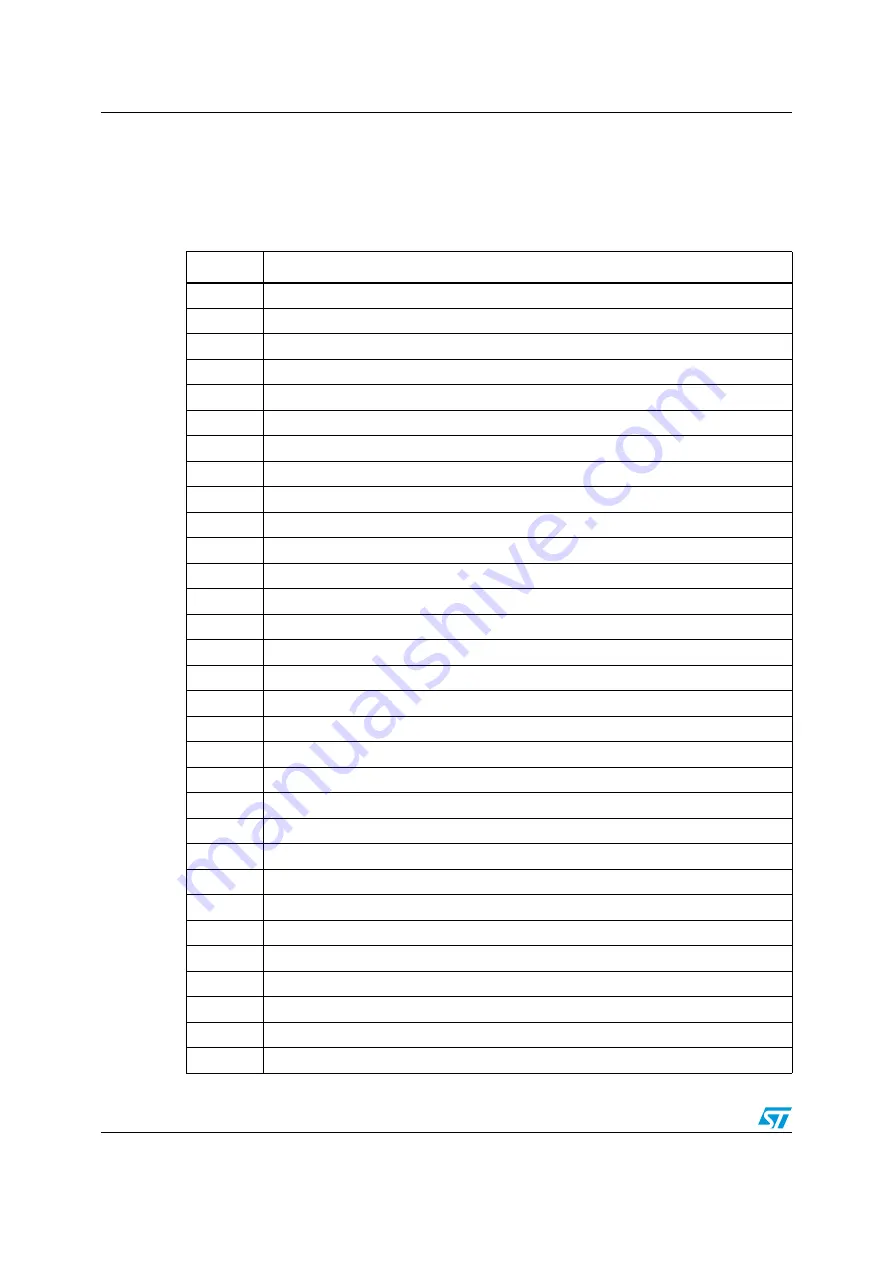

1 Acronyms

The below table contains acronyms and abbreviations that are used in this document.

Table 1.

Acronyms

Terms

Expansion

ADC

Analog to Digital Convertor

AES

Advanced Encryption Standard

AFE

Analog Front End

ALU

Arithmetic Logic Unit

ASIC

Application Specific Integrated Circuit

AS

Application Subsystem

AMBA

Advanced Micro controller Bus Architecture

AHB

AMBA High speed Bus

APB

Advanced Peripheral Bus

BIST

Built-In Self Test

BS

Basic Subsystem

CBC

Cipher Block Chaining

CTR

Counter

CMOS

Complimentary Metal-Oxide Semiconductor.

CRC

Cyclic Redundancy Check

DAC

Digital to Analog Convertor

DES

Data Encryption Standard

DLL

Data Link Layer

DMA

Direct Memory Access

DDR

Double Data Rate

ECB

Electronic Code Book

EHCI

Enhanced Host Controller Interface

FIFO

First-In-First-Out

FPGA

Field Programmable Gate Array

FSMC

Flexible Static Memory Controller

GPIO

General Purpose Input Output

HS

High speed Subsystem

IEEE

Institute of Electrical and Electronics Engineers

ISO

Isochronous

JPEG

Joint Photographic Experts Group

JTAG

Joint Test Action Group