VIM Control Registers

536

SPNU503C – March 2018

Copyright © 2018, Texas Instruments Incorporated

Vectored Interrupt Manager (VIM) Module

15.8.13 Wake-Up Enable Clear Registers (WAKEENACLR[0:2])

The wake-up enable clear registers (WAKEENACLRx) selectively disables individual wake-up interrupt

request lines.

,

,

and

describe these registers.

Figure 15-32. Wake-Up Enable Clear Register 0 (WAKEENACLR0) [offset = 60h]

31

16

WAKEENACLR0[31:16]

R/WP-FFFFh

15

0

WAKEENACLR0[15:0]

R/WP-FFFFh

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -

n

= value after reset

Figure 15-33. Wake-Up Enable Clear Register 1 (WAKEENACLR1) [offset = 64h]

31

16

WAKEENACLR1[63:48]

R/WP-FFFFh

15

0

WAKEENACLR1[47:32]

R/WP-FFFFh

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -

n

= value after reset

Figure 15-34. Wake-Up Enable Clear Register 2 (WAKEENACLR2) [offset = 68h]

31

16

WAKEENACLR2[95:80]

R/WP-FFFFh

15

0

WAKEENACLR2[79:64]

R/WP-FFFFh

LEGEND: R/W = Read/Write; WP = Write in privilege mode only; -

n

= value after reset

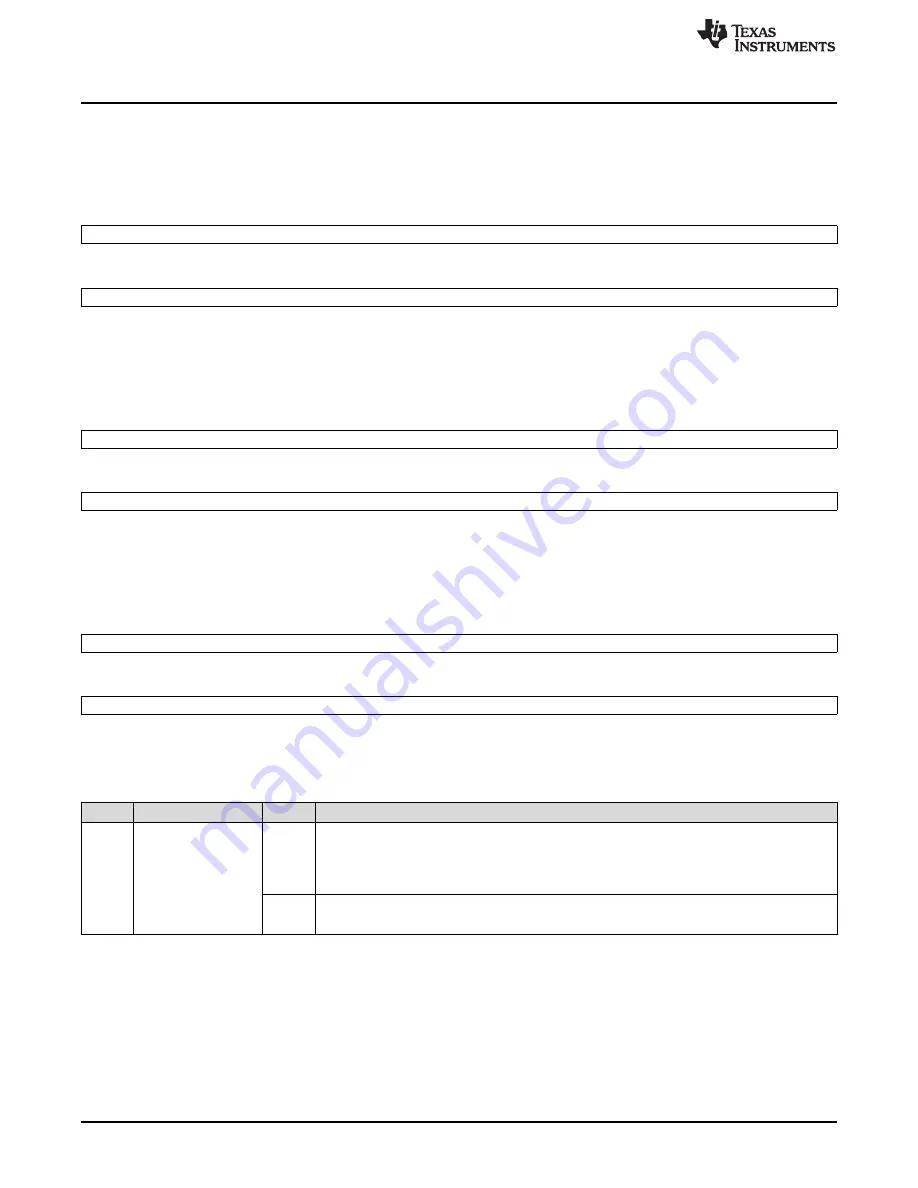

Table 15-14. Wake-Up Enable Clear Registers (WAKEENACLRx) Field Descriptions

Bit

Field

Value

Description

95-0

WAKEENACLRx[95:0

]

Wake-up enable clear bits. This vector determines whether the wake-up interrupt line is

enabled. Bit WAKEENACLRx[95:0] corresponds to interrupt request channel[95:0].

0

Read: Wake-up interrupt channel is disabled.

Write: A write of 0 has no effect.

1

Read: The wake-up interrupt channel is enabled.

Write: The wake-up interrupt channel is disabled.