688

/

838

Nations Technologies Inc.

Tel

:

+86-755-86309900

:

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

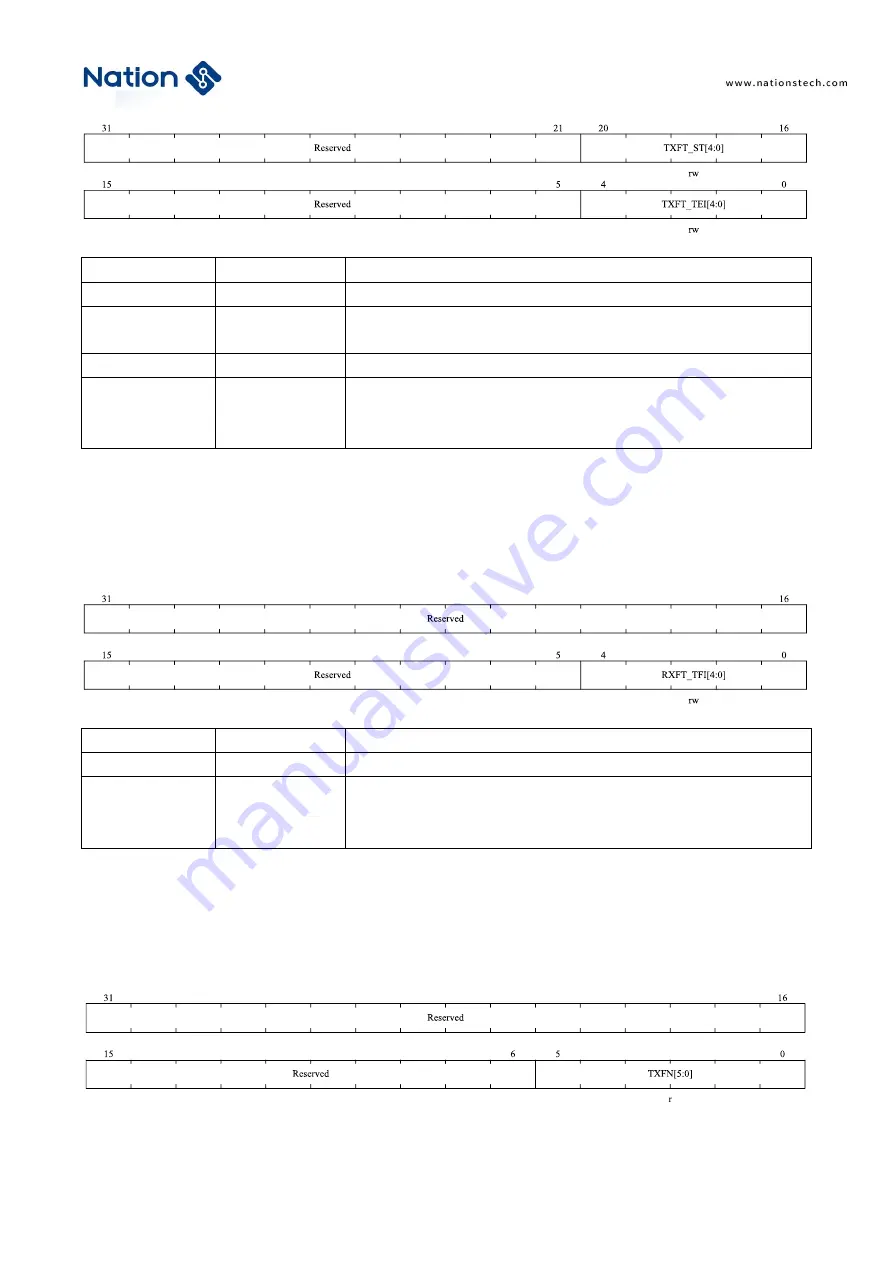

Bit field

Name

Description

31:21

Reserved

Reserved, the reset value must be maintained

20:16

TXFT_ST[4:0]

Transmit FIFO Threshold to Start to Transfer.

Tx transmission threshold, after reaching this value, start Tx transmission.

15:5

Reserved

Reserved, the reset value must be maintained

4:0

TXFT_TEI[4:0]

Transmit FIFO Threshold to Trigger Empty Interrupt.

Tx transmission threshold, when the number of transmit FIFOs is less than this

value, an empty interrupt is triggered.

24.6.9

QSPI Receive FIFO Threshold Level Register (QSPI_RXFT)

Address offset: 0x1C

Reset value: 0x0000 0000

Bit field

Name

Description

31:5

Reserved

Reserved, the reset value must be maintained

4:0

RXFT_TFI[4:0]

Receive FIFO Threshold to Trigger Full Interrupt.

Rx transmission threshold, when the number of receive FIFO is greater than this

value plus 1, a full interrupt is triggered.

24.6.10

QSPI Transmit FIFO Level Register (QSPI_TXFN)

Address offset: 0x20

Reset value: 0x0000 0000