General-purpose timers (TIM2/TIM3/TIM4)

RM0365

575/1080

DocID025202 Rev 7

The timer is able to generate PWM in edge-aligned mode or center-aligned mode

depending on the CMS bits in the TIMx_CR1 register.

PWM edge-aligned mode

Upcounting configuration

Upcounting is active when the DIR bit in the TIMx_CR1 register is low. Refer to

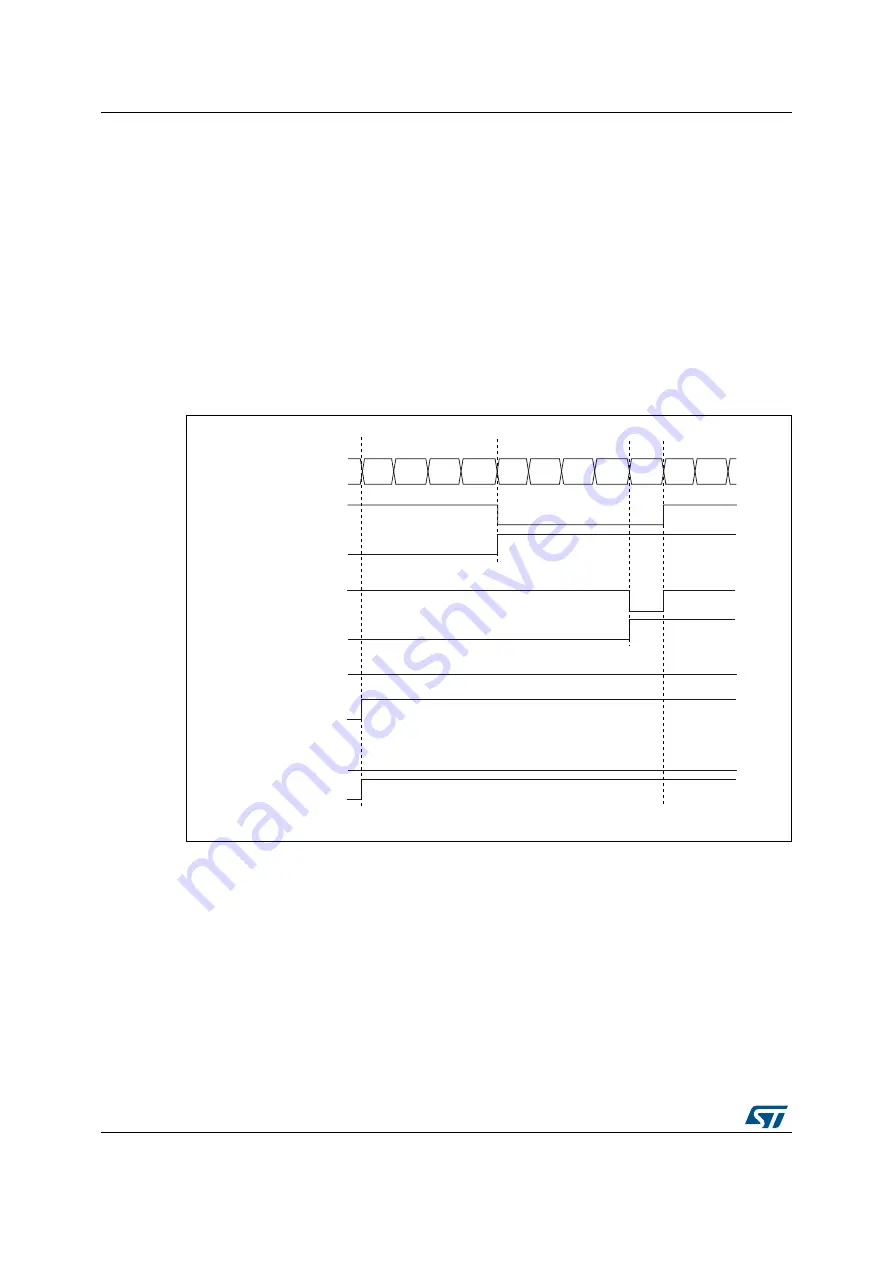

In the following example, we consider PWM mode 1. The reference PWM signal OCxREF is

high as long as TIMx_CNT <TIMx_CCRx else it becomes low. If the compare value in

TIMx_CCRx is greater than the auto-reload value (in TIMx_ARR) then OCxREF is held at ‘1.

If the compare value is 0 then OCxREF is held at ‘0.

shows some edge-aligned

PWM waveforms in an example where TIMx_ARR=8.

Figure 219. Edge-aligned PWM waveforms (ARR=8)

Downcounting configuration

Downcounting is active when DIR bit in TIMx_CR1 register is high. Refer to

In PWM mode 1, the reference signal ocxref is low as long as TIMx_CNT>TIMx_CCRx else

it becomes high. If the compare value in TIMx_CCRx is greater than the auto-reload value in

TIMx_ARR, then ocxref is held at 100%. PWM is not possible in this mode.

PWM center-aligned mode

Center-aligned mode is active when the CMS bits in TIMx_CR1 register are different from

‘00 (all the remaining configurations having the same effect on the ocxref/OCx signals). The

069

&RXQWHUUHJLVWHU

µ¶

2&;5()

&&[,)

2&;5()

&&[,)

2&;5()

&&[,)

2&;5()

&&[,)

&&5[

&&5[

&&5[!

&&5[

µ¶